## Faizal Arya Samman

# Microarchitecture and Implementation of Networks-on-Chip with a Flexible Concept for Communication Media Sharing

TECHNISCHE UNIVERSITÄT DARMSTADT

FACHBEREICH ELEKTROTECHNIK UND INFORMATIONSTECHNIK

D17

Darmstädter Dissertationen

2010

#### SAMMAN, Faizal Arya.

"Microarchitecture and Implementation of Networks-on-Chip with a Flexible Concept for Communication Media Sharing". *Technische Universität Darmstadt*, Dissertation (Doctoral Thesis), 2010.

Keywords:

Network-on-Chip,

VLSI Microarchitecture,

Wormhole Cut-Through Switching,

Theory for Deadlock-Free Multicast Routing,

Tree-based Multicast Routing,

Runtime Adaptive Routing Selection Strategy,

Contention- and Bandwidth-Aware Adaptive Routing,

Connection-Oriented Communication,

Guaranteed-Bandwidth Service.

Copyright © 2010 by Faizal Arya Samman

Published in Germany.

# Microarchitecture and Implementation of Networks-on-Chip with a Flexible Concept for Communication Media Sharing

Vom Fachbereich 18

Elektrotechnik und Informationstechnik

der Technischen Universität Darmstadt

zur Erlangung der Würde eines

Doktor–Ingenieurs (Dr.-Ing.)

genehmigte Dissertation

von

M.T. Faizal Arya Samman

geboren am 05. 06. 1975 in Makassar, Indonesien

Referent: Prof. Dr. h. c. mult. Manfred Glesner

Technische Universität Darmstadt

Korreferent: Prof. Dr.-Ing. Hans Eveking

Technische Universität Darmstadt

Tag der Einreichung: 26. 01. 2010

Tag der mündlichen Prüfung: 08. 06. 2010

D17

Darmstadt 2010

for my lovely Mother, my Father, and my Family

## Acknowledgment

This thesis is based on my work that I have started in October 2006 at Fachgebiet Mikroelektronische Systeme, Institut für Datentechnik, Fachbereich Elektrotechnik und Informationstechnik, Technische Universtät Darmstadt as a research assistant with a scholarship from DAAD (Deutscher Akademischer Austausch-Dienst). Therefore, I would like to thank the DAAD for awarding me the scholarship to pursue my doctoral degree. Special thanks are due to my advisor Prof. Dr. Dr. h.c. mult. Manfred Glesner for his advices, guidances and nice working environment. The colourful working atmosphere at his research institute reflects his internationally open personality, quality and care, from which I have benefited.

As my co-advisor, I express my acknowledment to Prof. Dr.-Ing. Hans Eveking for his supports and advices. I would like to thank Prof. Dr.-Ing. Gerd Balzer, Prof. Dr.-Ing. habil. Roland Werthschützky and Prof. Dr.rer.nat. Andy Schürr for spending time to be the committee of my oral examination. I would like to acknowledge Prof. Dr. Ir. Nadjamuddin Harun, Ir. Rhiza S. Sadjad, MSEE, PhD and Ir. Eniman Y. Syamsuddin, MSc, PhD for their recommendations to pursue higher educational degree that is useful for my academical career. Furthermore, I would also like to thank Prof. Dr.-Ing. Holger Hanselka and Prof. Dr.-Ing. Thilo Bein as the project coordinator and manager of the AdRIA (Adaptronik–Research, Innovation, Application) Project, in which I can continue my post-doctoral research experience at *Technische Universtät Darmstadt* in collaboration with *LOEWE-Zentrum, Fraunhofer Institut für System-Zuverlässigkeit und Betriebfestigkeit*.

I gratefully acknowledge Dr.-Ing. Thomas Hollstein who has spent much time with me to discuss and share technical knowledge about network-on-chip (NoC) topic with a fruitful discussion until I can really understand the topic which is a new topic for me as I just came to the *Fachgebiet Mikroelektronische Systeme*. I thank Prof. Dr.-Ing. Peter Zipf and Dr.-Ing. Leandro S. Indrusiak for the time to discuss about NoC topic in the particular area of system-level design, as well as to all anonymous reviewers of my journal and conference papers for the positive critics and suggestions.

Many thanks are due to the former staff members at *Fachgebiet Mikroelektronische Systeme*, Dr.-Ing. Tudor Murgan, Dr.-Ing. Oliver Soffke, Dr.-Ing. Oana M. Cobianu, Dr.-Ing. Andre Guntoro, Dr.-Ing. Massoud Momeni, Wang Hao, Heiko Hinkelmann as well as to the current staff members, Petru Bacinschi, Enkhbold Ochirsuren, Christopher Spies, Hans-Peter Keil, Surapong Pongyupinpanich, François Philipp, Ping Zhao, Leandro Möller and Sebastina Pankala for the friendships and cooperations. I would also like

to express my appreciation to the staff members at *Fachgebiet Integrierte Elektronische Systeme*, the head of the institute Prof. Dr.-Ing. Klaus Hofmann and his research and teaching assistant staff. My acknowledgements are granted to Andreas Schmidt and Roland Brand for helping me in many thing about software and hardware matters, and to Silvia Hermann and Iselona Klenk for helping me in many administrative matters.

I express my gratitude to all my supervised students, Youness Sennani, Lufei Shen, Jonatan Antoni, Souhaili Rhazi, Shengtian Le, Björn Dollak and Florian B. Luley, who have made nice cooperations with me in the framework of bachelor/master/diploma thesis. Thank you very much also to Abdul Hakim Hamid for proof-reading and correcting this written-english thesis. My stay in Darmstadt is enhanced by many friends. For the fruitful friendships, I appreciate all my Colleagues from Indonesia, Germany and from all other countries that I could not mention them in this pages.

I deeply acknowledged all my teachers in my primary school, secondary school and my high school in Sungguminasa, Gowa, as well as my lecturers at *Universitas Gadjah Mada* in Yogyakarta and at *Institut Teknologi Bandung* for providing me with basic and advanced knowledge. Many thanks are also given to all teaching, technical and administrative staff members at *Universitas Hasanuddin* in Makassar for their helps and administrative supports.

From the depth of my heart, I am grateful to my lovely mother and my lovely father for their patience to advice and educate me. Their love, care, dedication and their long-life educational supports cannot be expressed with words. I pray for them to be blessed, and their prayer is a strong motivation for me to make them proud. I am also deeply grateful to my lovely wife Wahyuni Sirajuddin for her love, supports and her best care. Special thanks are deeply due to my lovely children Syifa Marabintang, Imam Manggarai and Alya Deapati for their love and patience, for having a busy father. I would also like to thank my brothers Zulfikar Adijana, Tajul Arifin, and my Sisters Azmi Adiarti, Aida Mardiah, Yuyun Zulaena, as well as all my relationships for their supports and for taking care well our lovely mother during her life.

Last but not least, I thank God (*Allah*), All-Mighty, The Most Merciful, the Supreme in knowledge and power, and the Creator of the universe, Whom I have seeked His knowledge and His guidance from and to Whom He has given us life in this world so as to be beneficial to humanity before we go to an eternity life.

Darmstadt, July 2010

Faizal Arya Samman

### **Abstract**

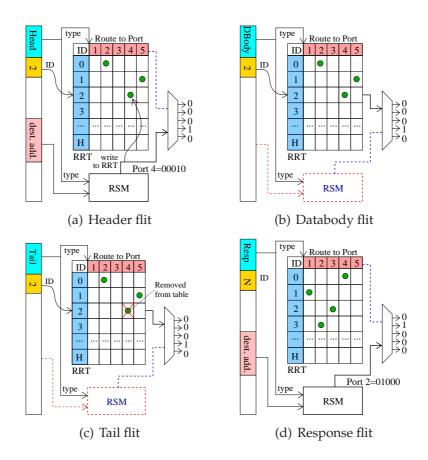

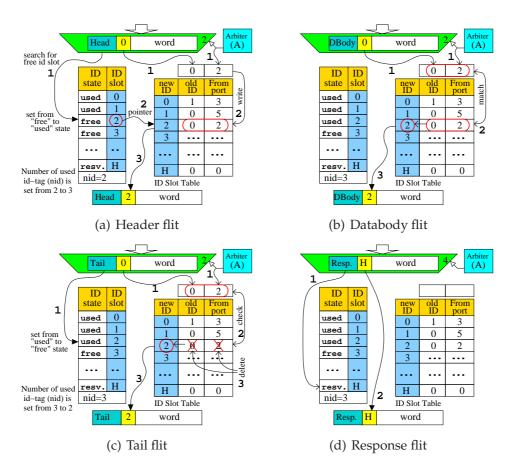

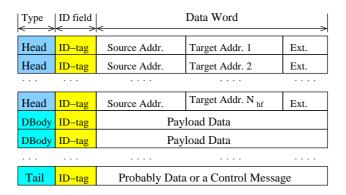

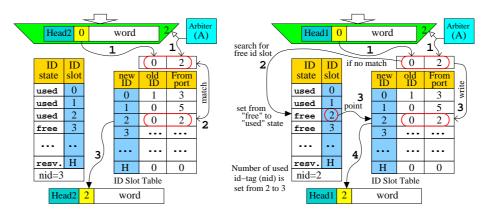

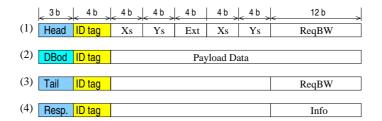

This thesis proposes a concept, VLSI microarchitecture and implementation of a network-on-chip (NoC) supporting a flexible communication media share methodology. The concept and methodology are based on a variable dynamic local identity tag (ID-tag) management technique, where different messages can be interleaved at flit-level on the same communication channel. Each message is multiplexed and allocated to a local ID slot on the shared channel. In order to implement the concept and methodology, a special packet format will be introduced, where additional two control bit fields, i.e. an ID-tag field and a flit-type field, are attached on every flit of the message in line with a data word. The reserved ID slot number, to which the message is allocated, is attributed in the ID-tag field. The flit-type field together with the ID-tag field is used to identify the messages and the type of every message flit, and to control the behavior of certain components in the NoC switch (NoC router) at runtime (during application execution time). The type of the flits is classified into a header used to open the ID-tag reservation, a databody, or a tail flit that is used to terminate the ID-tag reservation.

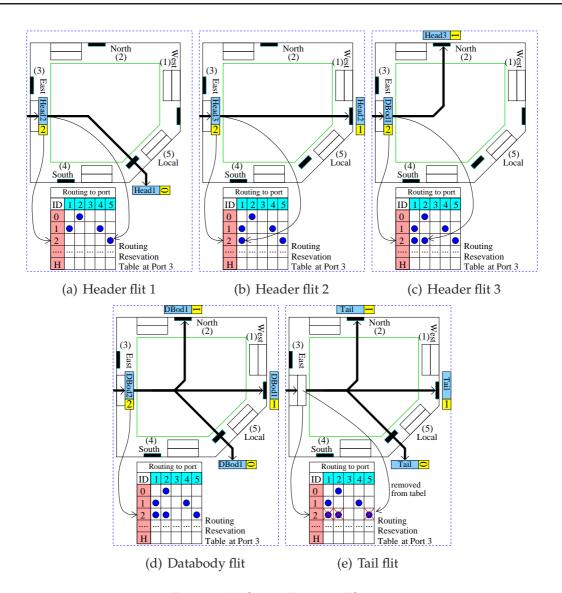

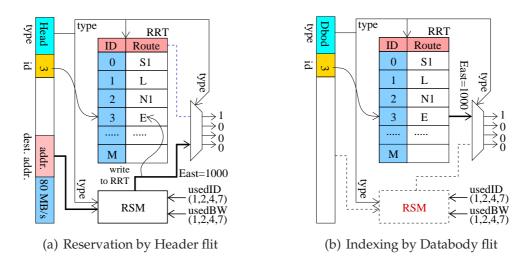

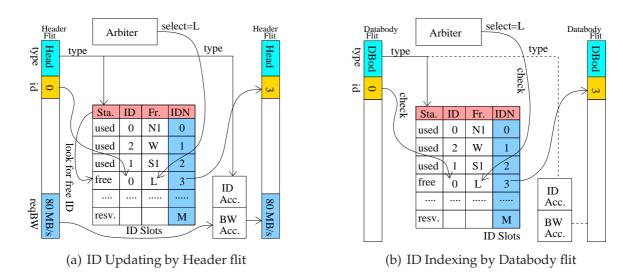

When entering a new communication channel, the ID-tag of a message is updated. Each message is allocated to a new local ID slot and organized in such a way, that flits belonging to the same message will have the same ID-tag on every communication channel. Therefore, an ID management unit is integrated in a switch multiplexor component at every output port of the NoC router to organize the ID-tag reservation or the ID slot allocation procedure. In order to guarantee a correct routing path configuration at runtime, a routing engine component consisting of a routing state machine and a routing reservation table is implemented on each input port. The routing engine routes the interleaved different messages based on their ID-tag.

The proposed concept and methodology have impacts on the implementation of advantageous and extensive features in the NoC router compared with the existing NoC concepts presented in the literature. The basic advantageous application of the proposed concept and methodology is the ability to implement a new wormhole switching method called *wormhole flit-level cut-through switching method* to overcome the head-of-line blocking problems commonly occur when using traditional wormhole switching method. The problem is solved by allowing the flits of the competing wormhole messages to be interleaved at flit level in the same communication link without using virtual channels.

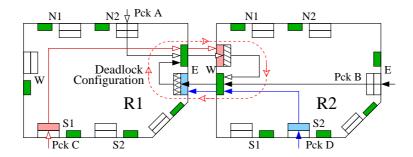

The proposed concept allows us to implement a new deadlock-free tree-based mul-

ticast routing methodology with static or adaptive routing algorithm, where the routing engines used to route the unicast and multicast messages are the same, resulting in a low-area overhead multicast routing engine. The thesis introduces also a *new theory for deadlock-free multicast routing* suitable for NoCs. The theory is formulated based on a new simple and smart mechanism to handle multicast contentions called *hold-release tagging mechanism*. The multicast deadlock configuration problem in the tree-based multicast routing is solved without the use of virtual channels.

Beside (1) the new wormhole switching method and (2) the new deadlock-free multicast routing method mentioned before, the proposed concept allow us, (3) to develop a new adaptive routing selection strategy (contention- and bandwidth-aware adaptive routing selection strategy), (4) to develop a switched virtual circuit configuration method based on the ID-division multiple access technique for implementing a runtime connection-oriented guaranteed-bandwidth service, and (5) to combine the connectionless best-effort and the connection-oriented guaranteed-bandwidth services in a single NoC router prototype.

This doctoral thesis introduces in general a NoC router prototype called **XHiNoC** (e**X**tendable **H**ierarchical **N**etwork-**o**n **C**hip). The VLSI microarchitecture of the XHiNoC routers is flexible and extendable, in which the generic components of the NoC router can be simply replaced by extended components. If needed, a number of new signal paths is added. Hence, a new NoC router prototype with the aforementioned extensive services, such as adaptive routing service, multicast routing service and connection-oriented guaranteed-bandwidth service can be designed from the basic VLSI microarchitecture of the XHiNoC Router.

## Kurzfassung

Diese Dissertation stellt ein Konzept für eine VLSI-Mikroarchitektur und Implementierung eines On-Chip Netwerks vor, welches eine flexible Nutzung von Routing-Ressourcen unterstützt. Das Konzept und die Methodologie basieren auf einer variablen lokalen Identität (ID-Tag) von Datenpaketen auf den einzelnen Segmenten des Routing-Netzwerks, wodurch eine gleichzeitige gefaltete Übertragung (Interleaving) mehrerer Datenpakete auf einem Datensegment ermöglicht wird. Hierfür wurde ein spezielles Format für die Flits eines Datenpakets entworfen, welches als zusätzliche Steuerungsinformationen für den Datenfluss Informationen über den Pakettyp und die lokale ID (ID-Tag) des Pakets auf dem aktuell betrachteten Routing-Segment enthält. Mit diesen Zusatzinformationen wird das Verhalten der On-Chip Router des Network-on-Chip (NoC) lokal gesteuert. Datenpakete bestehen aus Datenheader, Payload und einem Deskriptor für das Ende des Pakets.

Wenn ein Router einen Datenheader empfängt, trifft die aus einer kombinierten Routing-Zustandsmaschine und einer Routingtabelle bestehende Routing-Engine am Eingang des Routers eine Entscheidung für die Richtung der Weiterleitung des Pakets und ein eingebauter ID-Manager ordnet dem Paket eine freie ID auf dem ausgehenden Routing-Segment zu. Alle nachfolgenden Flits des Datenpakets werden über deren ID auf dem Dateneingangssegment erkannt, automatisch auf dieses Ausgangs-Routingsegment geschaltet (Switching) und mit derselben lokalen ID versehen, die auch dem Header des Pakets zugeordnet wurde. Passiert ein Paketende einen Router, so wird die für das Paket verwendete lokale ID wieder freigegeben. Die ID-Verwaltung und -Vergabe wird mit Hilfe eines Steuerungsmoduls realisiert, das in den Multiplexern des On-Chip Routers integriert ist.

Im Vergleich zu Konzepten der anderer bekannter On-Chip Netzwerke, haben das vorgeschlagene Konzept und die implementierte Methodologie Vorteile im Hinblick auf eine effiziente Implementierung der On-Chip-Router. Basierend auf dem vorgeschlagenen Konzept können Wormhole-Routingverfahren mit wesentlicher Reduktion der hierbei üblichen Warteschlangen-Blockierungsprobleme implementiert werden. Flits verschiedener Datenpakete können auf dem gleichen Übertragungskanal gemischt werden, wofür keine expliziten virtuellen Datenkanäle benötigt werden, was zu einer erheblichen Reduktion der Größe von Datenpuffern führt.

Das vorgeschlagene Konzept ermöglicht es weiterhin, eine blockierungsfreie Multicast-

Routingsmethode mit einem statischen oder adaptiven Routingsalgorithmus zu implementieren. In der vorliegen Dissertationsschrift wird auch eine neue blockierungsfreie Multicastroutingstheorie vorgestellt, die sich für On-Chip Netzwerke eignet und auf dem beschriebenen Grundkonzept basiert. Die hiervon abgeleitete Methodik ist als sogenannter "Hold-Release-Tagging-Mechanismus" implementiert, und löst das Problem einer möglichen gleichzeitigen Konkurrenz von Datenwörtern um eine bestimmte Ausgangsressource eines Netzwerkrouters. Letzteres stellt insbesondere bei Multicast-Datenkommunikation ein schwerwiegendes Problem dar und wird hier ohne Verwendung virtueller Kanäle gelöst.

Neben (1) der neuen Wormhole-Paketvermittlungsmethode und (2) dem neuen Multicastroutingverfahren, wird unter Verwendung des vorgeschlagenen Konzepts ermöglicht, (3) eine lastabhängige Bandbreitensteuerung lokal in den Routern vorzunehmen, (4) virtuelle Leitungsverbindungen ohne Notwendigkeit einer zentralen Steuereinheit für die Bereitstellung einer verbindungsorientierten Datenübertragung (Quality of Service) bereitzustellen, und (5) kombinierte verbindungslose (Datenpakete) und verbindungsorientierte (Streaming) Datenübertragung in einem on-Chip Router zu implementieren.

In dieser Dissertation wird die NoC-Prototypenarchitektur XHiNoC (eXtendable Hierarchical Network-on Chip) vorgestellt. Die VLSI-Mikroarchitektur des XHiNoC-Routers ist flexibel und erweiterbar, wobei die generische Komponenten des NoC Routers einfach mit anderen erweiterten Komponenten ersetzt werden können. Daher können problemlos neue NoC-Routerprototypen generiert werden, die zusätzliche Dienste, wie die oben genannten Dienste (adaptive Routingsverfahren, Multicast-Routingsverfahren oder verbindungsorientierte Datenübertragung mit Bandbreitengarantie) bereitstellen. Basierend auf der XHiNoC-Architektur können in kürzester Zeit bedarfsangepasste Router erstellt werden, die nur die benötigten Dienste bei minimiertem Overhead abbilden. Da die ganze Architektur auf einen globalen Controller verzichtet, ist sie beliebig skalierbar. Aufgrund der verwendeten Steuerung der Dateninjektion werden die im Netzwerk injizierten Datenmengen der verfügbaren Übertragungskapazität angepasst, womit eine wesentliche Reduktion der Datenpuffer und routerinternen Steuerungsmechanismen einhergeht.

# **Table of Contents**

| 1 | Intr | oductio | on and Overview                                          | 1  |

|---|------|---------|----------------------------------------------------------|----|

|   | 1.1  | Backg   | round and Motivations                                    | 1  |

|   | 1.2  | Resea   | rch Scope and Objectives                                 | 3  |

|   | 1.3  | Thesis  | S Outline                                                | 4  |

| 2 | On-  | Chip I1 | nterconnection Networks                                  | 7  |

|   | 2.1  | Netwo   | ork-on-Chip Topology Architecture                        | 11 |

|   |      | 2.1.1   | Mesh-Like Network Topology                               | 13 |

|   |      | 2.1.2   | Tree-based Network Topology                              | 14 |

|   |      | 2.1.3   | Irregular or Custom Network Topology                     | 15 |

|   |      | 2.1.4   | Other Network Topologies                                 | 15 |

|   |      | 2.1.5   | Hybrid and Hierarchical Network Topology                 | 16 |

|   | 2.2  | Gener   | ric On-Chip Switch Architecture                          | 17 |

|   | 2.3  | Switch  | hing Methodology                                         | 19 |

|   |      | 2.3.1   | Packet Switching (Store-and-Forward)                     | 19 |

|   |      | 2.3.2   | Wormhole Switching                                       | 20 |

|   |      | 2.3.3   | Virtual Cut-Through Switching                            | 21 |

|   |      | 2.3.4   | Circuit Switching                                        | 22 |

|   | 2.4  | Routin  | ng Algorithms                                            | 22 |

|   |      | 2.4.1   | Deadlock and Livelock Configuration                      | 22 |

|   |      | 2.4.2   | Taxonomy of Routing Algorithms                           | 23 |

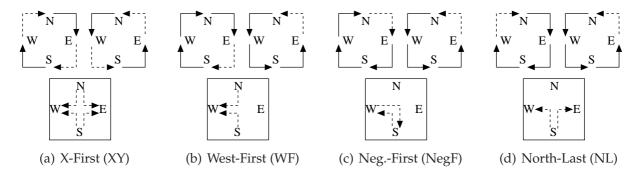

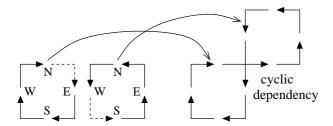

|   |      | 2.4.3   | Routing Algorithms based on Turn Models                  | 25 |

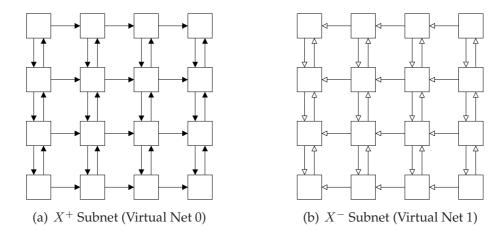

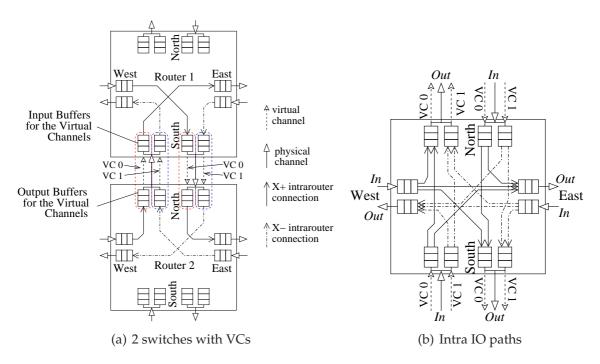

|   |      | 2.4.4   | Routing Algorithms with Virtual Channels                 | 29 |

|   | 2.5  | Perfor  | rmance Evaluation                                        | 32 |

|   |      | 2.5.1   | Performance Measurement Metrics                          | 32 |

|   |      | 2.5.2   | Workload Models                                          | 34 |

|   | 2.6  | Resea   | rch Fields Related to Networks-on-Chip                   | 35 |

|   |      | 2.6.1   | NoC Quality-of-Service                                   |    |

|   |      | 2.6.2   | NoC in Globally-Asynchronous Locally-Synchronous Context | 37 |

xiv Table of Contents

|   |     | 2.6.3    | NoC Application Mapping                                         | 40 |

|---|-----|----------|-----------------------------------------------------------------|----|

|   |     | 2.6.4    | NoC-based Multiprocessor Systems and Parallel Programming       | 42 |

|   |     | 2.6.5    | Testing Methods for NoC-based Multiprocessor Systems            | 44 |

|   |     | 2.6.6    | ASIC and FPGA Implementation Issue                              | 45 |

|   |     | 2.6.7    | Advanced NoC Research Issues                                    | 46 |

|   | 2.7 | Summ     | nary                                                            | 46 |

| 3 | Ove | erview o | of the On-Chip Router                                           | 49 |

|   | 3.1 | Design   | n Concept                                                       | 50 |

|   |     | 3.1.1    | Media Sharing with Local ID Management                          | 51 |

|   |     | 3.1.2    | Main Issue Related to Local ID Slots Availability               | 54 |

|   | 3.2 | Gener    | ric VLSI Architecture                                           | 56 |

|   |     | 3.2.1    | First-In First-Out Buffers                                      | 59 |

|   |     | 3.2.2    | Routing Engines                                                 | 64 |

|   |     | 3.2.3    | Arbitration Unit                                                | 67 |

|   |     | 3.2.4    | Crossbar Multiplexor with ID Management Unit                    | 68 |

|   | 3.3 | Chara    | acteristics and Features                                        | 72 |

|   |     | 3.3.1    | Pipeline Architecture                                           | 72 |

|   |     | 3.3.2    | Simultaneous Parallel Data Input-Output Intra-Connection        | 73 |

|   |     | 3.3.3    | Link-Level Flit Flow Control                                    | 75 |

|   |     | 3.3.4    | Saturating and Non-Saturating Conditions                        | 77 |

|   |     | 3.3.5    | Special Features of the XHiNoC                                  | 79 |

|   | 3.4 | RTL S    | imulator Infrastructure                                         |    |

|   |     | 3.4.1    | Traffic Pattern Generator                                       | 80 |

|   |     | 3.4.2    | Traffic Response Evaluator                                      | 81 |

|   |     | 3.4.3    | Performance Evaluation Graphs                                   |    |

|   | 3.5 | Summ     | nary                                                            | 83 |

| 4 | Wor | mhole    | Cut-Through Switching: Flit-Level Messages Interleaving         | 85 |

|   | 4.1 | Blocki   | ing Problem in Traditional Wormhole Switching                   | 86 |

|   | 4.2 | The N    | Jovel Wormhole Cut-Through Switching Method                     | 88 |

|   |     | 4.2.1    | Virtual-Channelles Solution with ID-based Multiple Access Tech- |    |

|   |     |          | nique                                                           | 89 |

|   |     | 4.2.2    | Packet Format                                                   | 91 |

|   |     | 4.2.3    | Correctness of the Routing Path Establishment                   | 92 |

|   |     | 4.2.4    | Switching Behaviors in Saturation and Non-Saturation            |    |

|   | 4.3 | Exper    | imental Results                                                 |    |

|   |     | 4.3.1    | Bit Complement Traffic Scenario                                 | 97 |

TABLE OF CONTENTS XV

|   |     | 4.3.2  | Hotspot Traffic Scenario                                          | 100 |

|---|-----|--------|-------------------------------------------------------------------|-----|

|   |     | 4.3.3  | Matrix Transpose Traffic Scenario                                 | 102 |

|   |     | 4.3.4  | Perfect Shuffle Traffic Scenario                                  | 103 |

|   |     | 4.3.5  | Bit Reversal Traffic Scenario                                     | 104 |

|   |     | 4.3.6  | Qualitative Comparisons with Traditional Wormhole Switching       | 105 |

|   |     | 4.3.7  | Queue-Depth-Insensitive Performance Behavior                      | 107 |

|   | 4.4 | Design | n Customization for Area Optimization                             | 108 |

|   |     | 4.4.1  | Neglecting Paths for Backtrace Routing                            | 109 |

|   |     | 4.4.2  | Neglecting Paths related to Prohibited Turns                      | 110 |

|   | 4.5 | Synth  | esis Results                                                      | 110 |

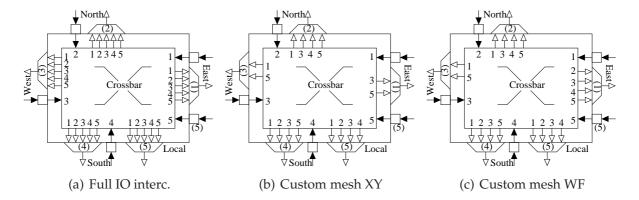

|   |     | 4.5.1  | Synthesis with Fully and Custom Crossbar IO Interconnects         | 110 |

|   |     | 4.5.2  | Synthesis with Different FIFO Queue Depths                        | 114 |

|   |     | 4.5.3  | Synthesis with Different Number of Available ID Slots             | 115 |

|   |     | 4.5.4  | Synthesis on an FPGA Device                                       | 116 |

|   | 4.6 | Summ   | nary                                                              | 116 |

|   |     |        |                                                                   |     |

| 5 | Mul |        | 3                                                                 | 117 |

|   | 5.1 | The N  | leed for Collective Communication                                 | 119 |

|   | 5.2 | State- | of-The-art in Multicast Routing Methodology and Theory            | 120 |

|   |     | 5.2.1  | Path-based and Tree-based Multicast Routing Methods               | 120 |

|   |     | 5.2.2  | Source and Distributed Multicast Routing                          | 122 |

|   | 5.3 | Theor  | y for Deadlock-Free Multicast Routing                             | 124 |

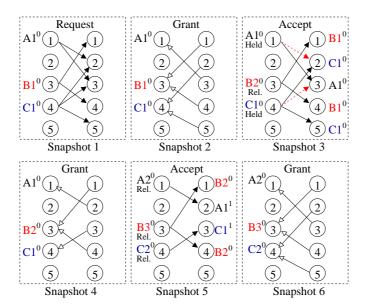

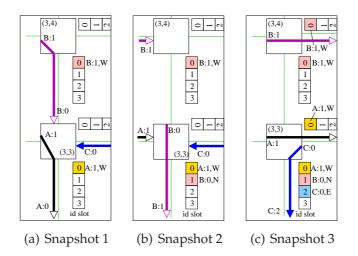

|   |     | 5.3.1  | New Multicast Method based on Hold-Release Tagging Policy         | 125 |

|   |     | 5.3.2  | Multicast Flit Replication Control based on Hold/Release Tagging  |     |

|   |     |        | Mechanism                                                         |     |

|   |     | 5.3.3  | Proof of the New Theory for Deadlock-Free Multicast Routing       | 133 |

|   | 5.4 |        | assed Multicast Router Implementation with Best-Effort Communica- | 405 |

|   |     |        | rotocol                                                           |     |

|   |     | 5.4.1  | Runtime Programming of Multicast Routing Reservation Table        |     |

|   |     | 5.4.2  | Runtime Multicast Local ID Slot Reservation                       |     |

|   | 5.5 | _      | tive Tree-based Multicast Routing                                 |     |

|   |     | 5.5.1  | 2D Planar Adaptive Routing Algorithm                              |     |

|   |     | 5.5.2  | Inefficient Spanning Tree Problem                                 |     |

|   | _   | 5.5.3  | Solution for the Inefficient Spanning Tree Problem                |     |

|   | 5.6 | -      | imental Result                                                    |     |

|   | 5.7 | -      | esis Results                                                      |     |

|   | 5.8 | Summ   | nary                                                              | 159 |

XVI TABLE OF CONTENTS

| 6 | Con | tentior | n- and Bandwidth-Aware Adaptive Routing Algorithm                | 161 |

|---|-----|---------|------------------------------------------------------------------|-----|

|   | 6.1 | Motiv   | ation Behind Adaptive Routing Implementation                     | 162 |

|   | 6.2 | State-  | of-the-Art in Adaptive Routing Strategy                          | 163 |

|   |     | 6.2.1   | Selection based on FIFO Queue Occupancy                          | 163 |

|   |     | 6.2.2   | Selection based on Bandwidth-Space Occupancy                     | 165 |

|   | 6.3 | Archi   | tectures and Algorithms for Adaptive Routing Selection Functions | 168 |

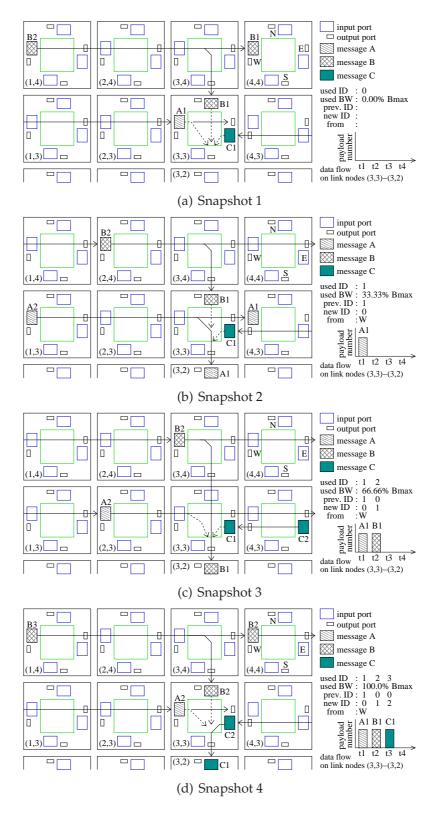

|   |     | 6.3.1   | Local ID-based Data Multiplexing                                 | 168 |

|   |     | 6.3.2   | Adaptive Routing Selection Functions                             | 168 |

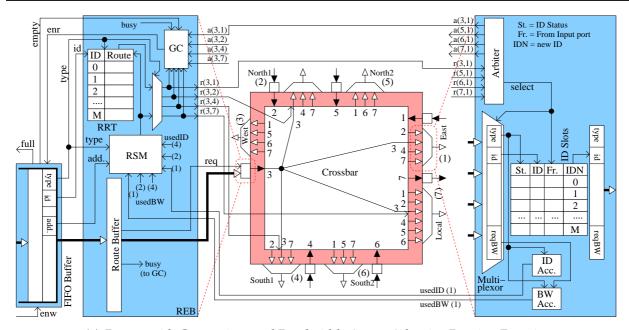

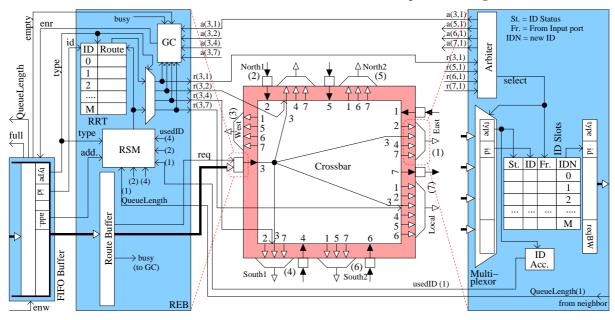

|   |     | 6.3.3   | Router Microarchitecture and Packet Format                       | 172 |

|   | 6.4 | Exper   | imental Results                                                  | 176 |

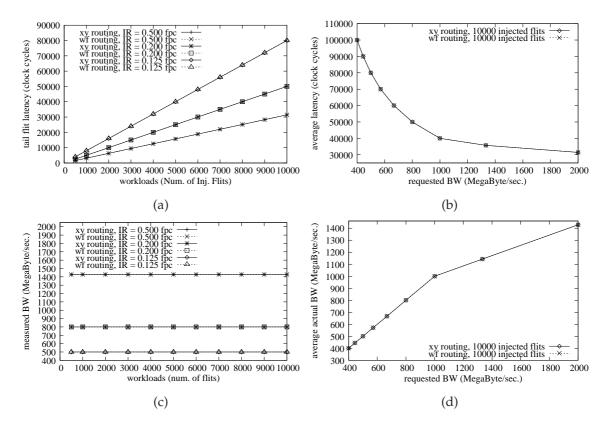

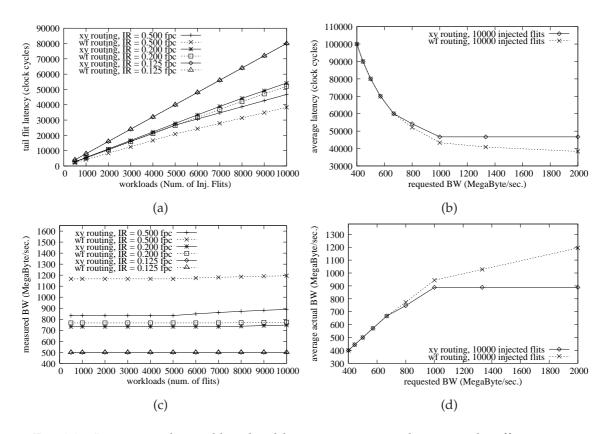

|   |     | 6.4.1   | Transpose Scenario in 4x4 Mesh Network                           | 176 |

|   |     | 6.4.2   | Bit Complement Scenario in 8x8 Mesh Network                      | 181 |

|   | 6.5 | Synth   | esis Results                                                     | 183 |

|   | 6.6 | Summ    | nary                                                             | 184 |

| 7 | Con | nection | n-Oriented Guaranteed-Bandwidth for Quality of Service           | 187 |

|   | 7.1 | State-  | of-the-art in Data Multiplexing Techniques For NoCs              | 188 |

|   |     | 7.1.1   | NoCs with TDMA Technique                                         | 188 |

|   |     | 7.1.2   | NoCs with SDMA Technique                                         | 188 |

|   |     | 7.1.3   | NoCs with CDMA Technique                                         | 189 |

|   |     | 7.1.4   | NoCs with IDMA Technique                                         | 189 |

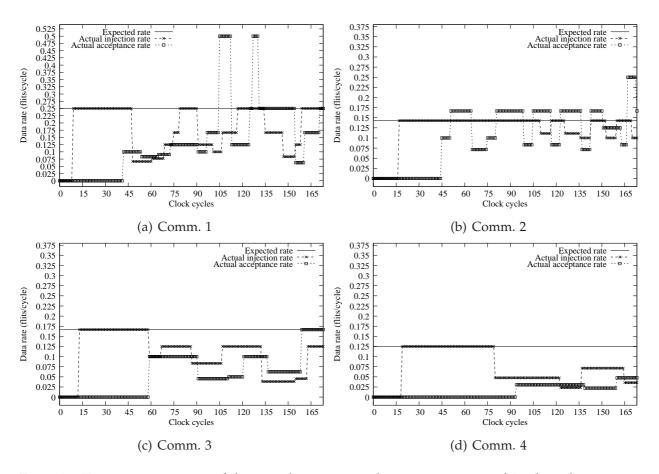

|   |     | 7.1.5   | Comparisons of the SVC Configuration Methods                     | 191 |

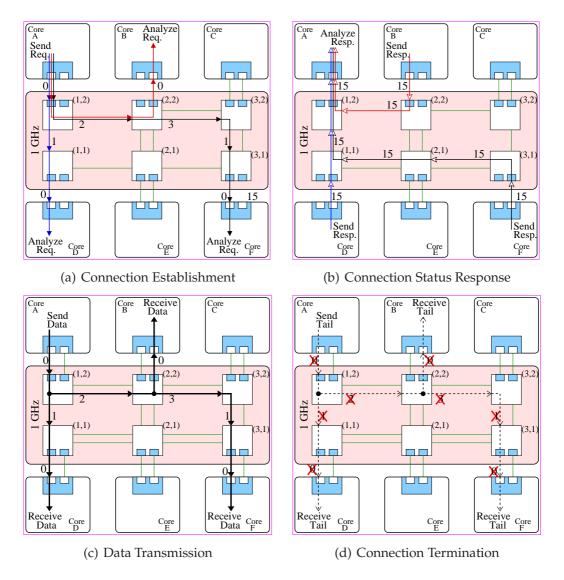

|   | 7.2 | Conne   | ection-Oriented Communication Protocol                           | 195 |

|   |     | 7.2.1   | Runtime Local ID Slot and Bandwidth Reservation                  | 196 |

|   |     | 7.2.2   | ID-based Routing Mechanism with Bandwidth Reservation            | 197 |

|   |     | 7.2.3   | Experiment on Radio System with Multicast Traffics               | 199 |

|   | 7.3 | Comb    | ined Best-Effort and Guaranteed-Throughput Services              | 203 |

|   |     | 7.3.1   | Microarchitecture for Combined GT-BE Services                    | 203 |

|   |     | 7.3.2   | The Difference of the Connectionless and Connection-Oriented Rou | ıt- |

|   |     |         | ing Protocols                                                    | 205 |

|   |     | 7.3.3   | Experiment with Combined GT-BE Traffics                          | 205 |

|   | 7.4 | Synth   | esis Results                                                     | 212 |

|   | 7.5 | Summ    | nary                                                             | 212 |

| 8 | Con | cludin  | g Remarks                                                        | 215 |

|   | 8.1 | Contr   | ibutions of the Work                                             | 215 |

|   | 8.2 | Direct  | ions for Future Works                                            | 217 |

| TABLE OF CONTENTS        | xvii |

|--------------------------|------|

| References               | 221  |

| List of Own Publications | 235  |

| Supervised Theses        | 239  |

| Curriculum Vitae         | 241  |

| Index                    | 247  |

# **List of Tables**

| 2.1 | Networks on Chip Prototypes                                                                                                                                                                                             | . 12  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.1 | The last flit acceptance (in $clock\ cycle\ period$ ) and average bandwidth (in $fpc/flit\ per\ cycle$ ) measurements for $Comm\ 1$ , $Comm\ 2$ and $Comm\ 3$ with different FIFO queue depths under transpose scenario | . 106 |

| 4.2 | The last flit acceptance (in $clock\ cycle\ period$ ) and average bandwidth (in $fpc/flit\ per\ cycle$ ) measurements for $Comm\ 4$ , $Comm\ 5$ and $Comm\ 6$ with different FIFO queue depths under transpose scenario | . 107 |

| 4.3 | Synthesis Results of the router with flit-level interleaved wormhole switching method using 130-nm CMOS technology with targeted working frequency of about $1.1~GHz$ (0.9 $ns$ clock period)                           | . 111 |

| 4.4 | Gate-level synthesis of the wormhole-switched router using 130-nm CMOS technology with 1.0 <i>GHz</i> target frequency (16 ID slots per link) for different FIFO buffer sizes (Queue-Depth)                             | . 114 |

| 4.5 | Gate-level synthesis of the wormhole-switched router using 130-nm CMOS technology (2-depth FIFO buffer) for different number of available ID slots per link                                                             | . 115 |

| 4.6 | Synthesis of the wormhole-switched router with customized crossbar IO interconnects on a Xilinx FPGA device (Target device: Spartan3 xc3s4000).                                                                         | . 116 |

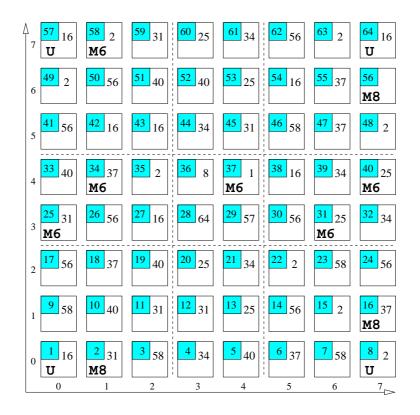

| 5.1 | Unicast and Multicast communication groups for the random multicast test traffic scenario                                                                                                                               | . 149 |

| 5.2 | Total performed traffics on each link direction for different tree-based static and adaptive multicast routing methods                                                                                                  | . 154 |

| 5.3 | Synthesis results of the multicast routers using 130-nm CMOS technology library                                                                                                                                         | . 158 |

| 6.1 | Synthesis results of the adaptive routers using 130-nm CMOS technology library                                                                                                                                          | . 186 |

| 7.1 | Flit types encoding for BE and GT packet services                                                                                                                                                                       | . 206 |

XX TABLE OF CONTENTS

| 7.2 | Synthesis results of t | he connection-oriented | l guaranteed-bandwidth | ı (GB) |

|-----|------------------------|------------------------|------------------------|--------|

|     | multicast routers usin | g 130-nm CMOS techn    | ology library          | 209    |

# **List of Figures**

| 2.1  | SoC Interconnect Communication Infrastructure                                                  | 9  |

|------|------------------------------------------------------------------------------------------------|----|

| 2.2  | Embedded multiprocessor system-on-chip (MPSoC) on mesh-connected NoC                           | 10 |

| 2.3  | Chip-Level multiprocessor (CMP) system on mesh-connected NoC                                   | 11 |

| 2.4  | Mesh-like networks.                                                                            | 13 |

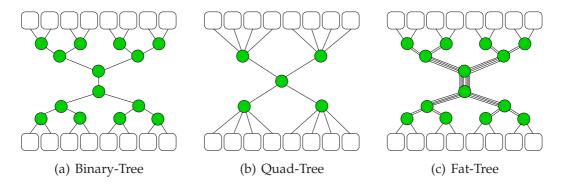

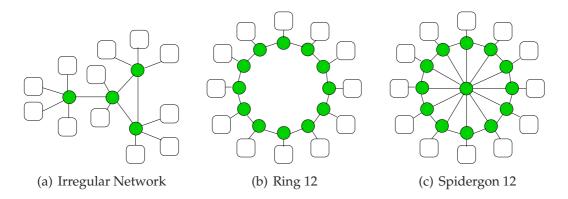

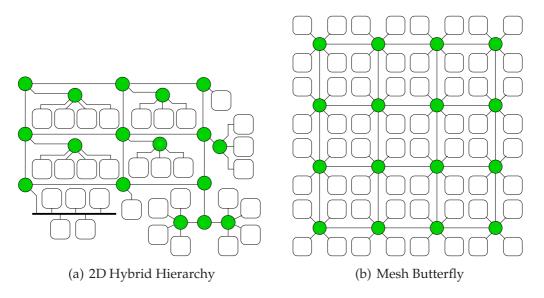

| 2.5  | Tree-based networks                                                                            | 14 |

| 2.6  | Irregular, Ring and Spidergon networks                                                         | 15 |

| 2.7  | Mesh butterfly and hybrid hierarchical networks                                                | 17 |

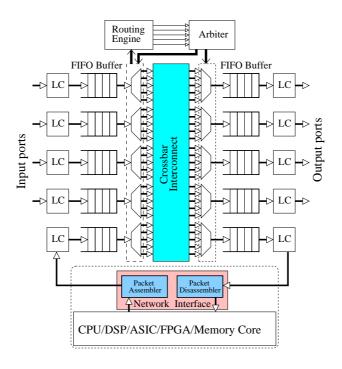

| 2.8  | Typical router structure                                                                       | 18 |

| 2.9  | Store-and-Forward Switching                                                                    | 19 |

| 2.10 | Wormhole Switching                                                                             | 20 |

| 2.11 | Virtual Cut-Through Switching                                                                  | 21 |

| 2.12 | Deadlock configuration                                                                         | 23 |

| 2.13 | Turn models that can avoid deadlock configuration                                              | 25 |

| 2.14 | Turn model that cannot avoid deadlock configuration                                            | 26 |

| 2.15 | Mesh Network separated into two virtual networks                                               | 30 |

| 2.16 | Two switches connected with virtual channels and the intra-IO interconnect paths of the switch | 31 |

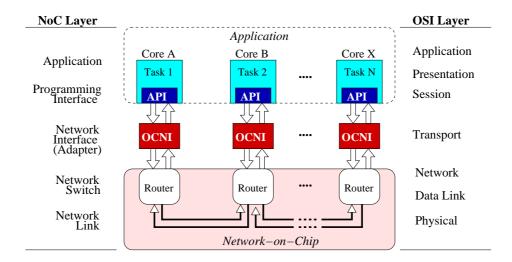

| 2.17 | NoC and OSI Model for interconnect protocol layers and the related NoC research areas          | 36 |

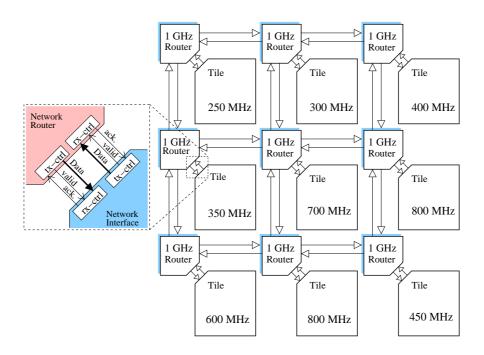

| 2.18 | Network-on-Chip-based multiprocessor system in GALS context                                    | 38 |

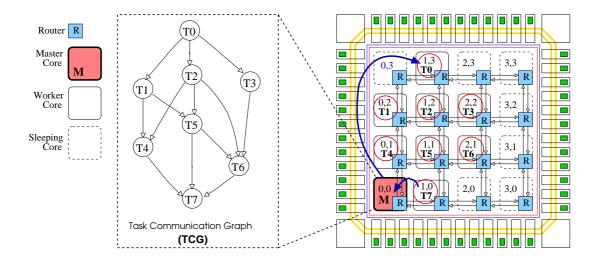

| 2.19 | Parallel task-based application mapping on the CMP System                                      | 41 |

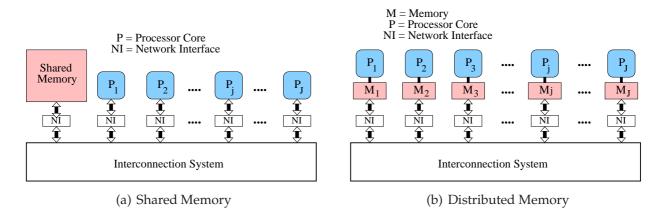

| 2.20 | Shared-memory and distributed-memory multiprocessor architecture                               | 42 |

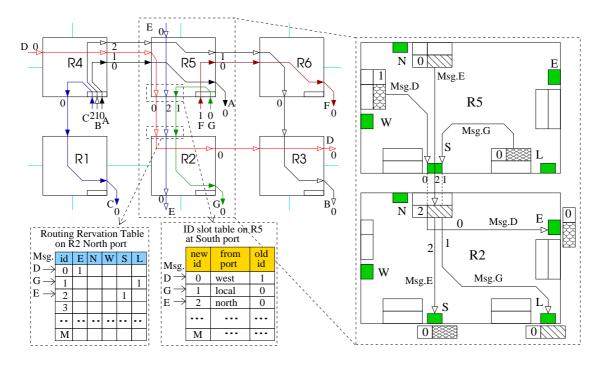

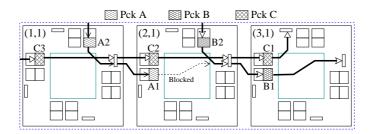

| 3.1  | Flexible concept view of the communication media share with local ID-tag management.           | 52 |

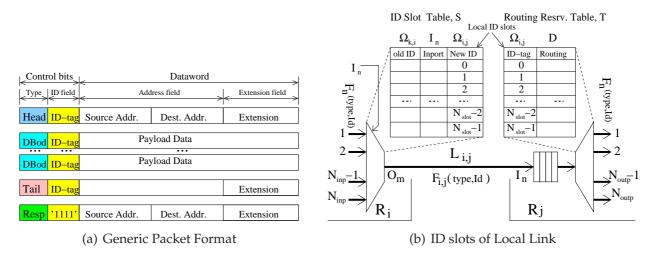

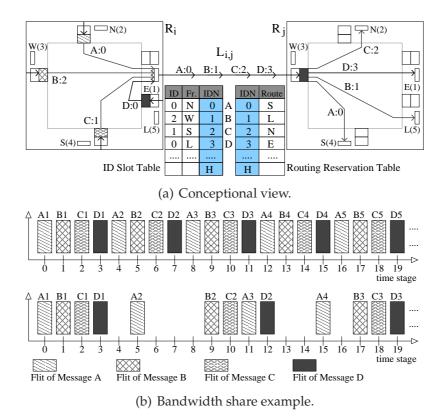

| 3.2  | The specific packet format and local ID slots                                                  | 54 |

xxii Table of Contents

| 3.3  | An example of the minimum number of available ID slots at two selected output ports when using minimal fully adaptive routing         | 55  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

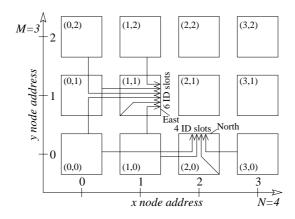

| 3.4  | An example of 2D $3 \times 3$ mesh network and a typical mesh router                                                                  | 56  |

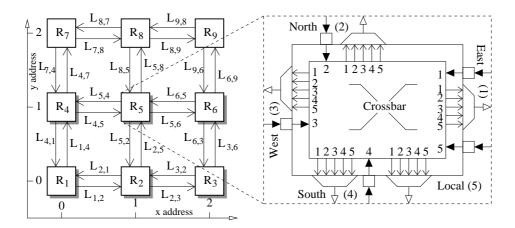

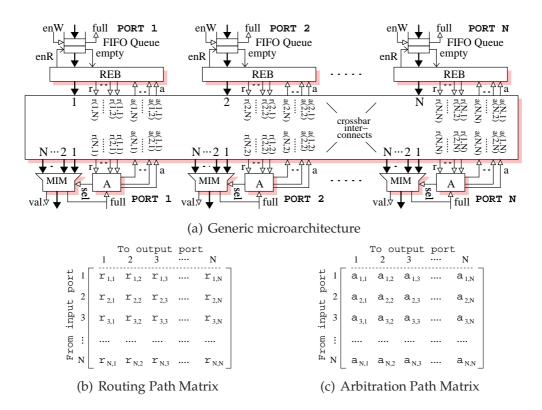

| 3.5  | Generic microarchitecture of the XHiNoC and the 2D array (matrix) representation of its routing and arbitration control paths         | 58  |

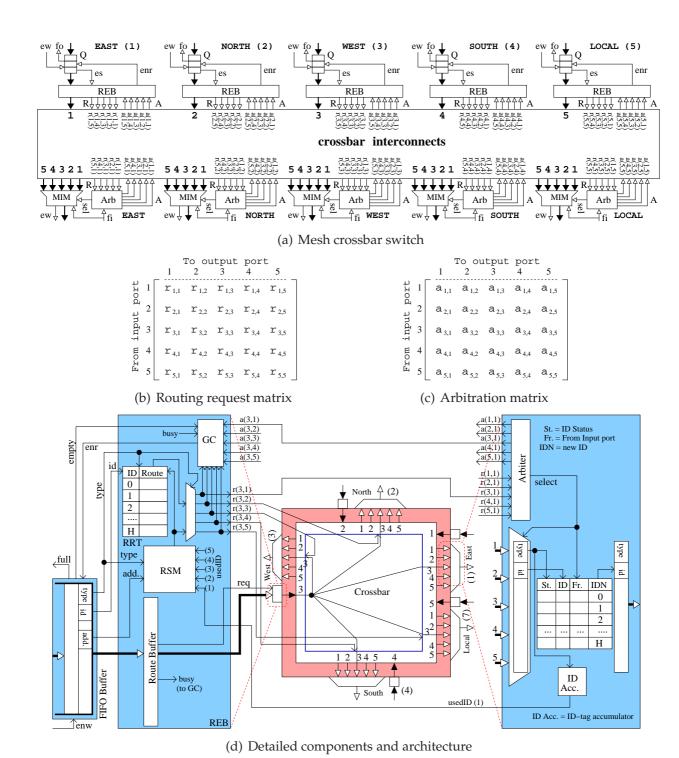

| 3.6  | Typical microarchitecture, routing request matrix, arbitration matrix and detail IO components of XHiNoC mesh router (5 IO ports)     | 60  |

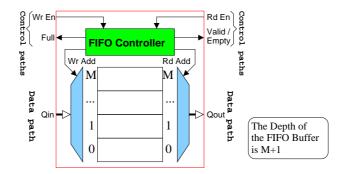

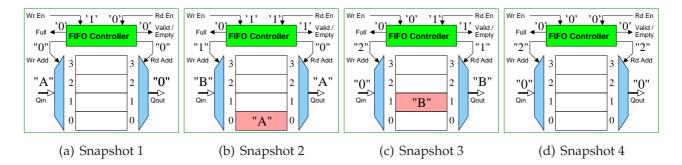

| 3.7  | The typical structure of the FIFO buffer                                                                                              | 61  |

| 3.8  | Examples of successive mode of operations in the FIFO buffer                                                                          | 63  |

| 3.9  | Local ID-based routing reservation and organization                                                                                   | 66  |

| 3.10 | Local ID-tag update and mapping management                                                                                            | 71  |

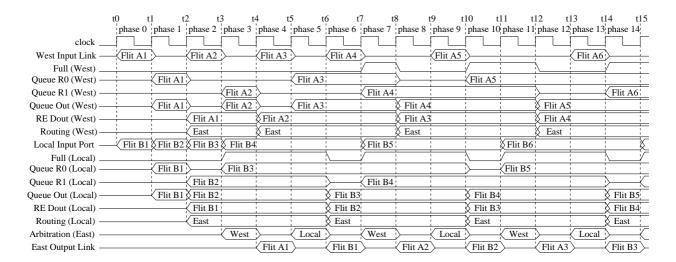

| 3.11 | Timing diagram (without contention) of the data switching and control paths.                                                          | 73  |

| 3.12 | Request-Grant-Accept mechanism to switch data in the XHiNoC router                                                                    | 74  |

| 3.13 | Link-level flit flow control in the XHiNoC                                                                                            | 76  |

| 3.14 | Timing diagram (with contention) of the data switching and control paths                                                              | 77  |

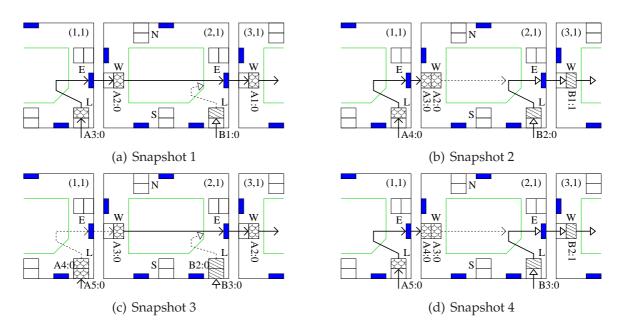

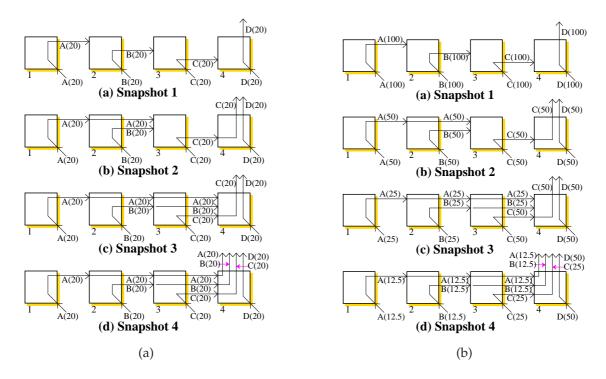

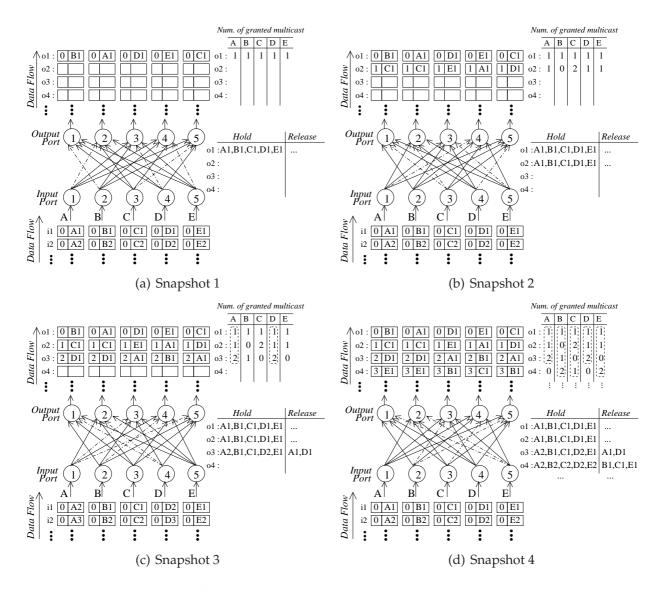

| 3.15 | Four snapshots of link bandwidth sharing situation (a) when the NoC is not saturated, and (b) when the NoC is saturated               | 78  |

| 4.1  | Head-of-line blocking problem in wormhole switching                                                                                   | 87  |

| 4.2  | Head-of-line blocking problem solution with 2 virtual channels per input port                                                         | 88  |

| 4.3  | Local ID-based Data Multiplexing                                                                                                      | 90  |

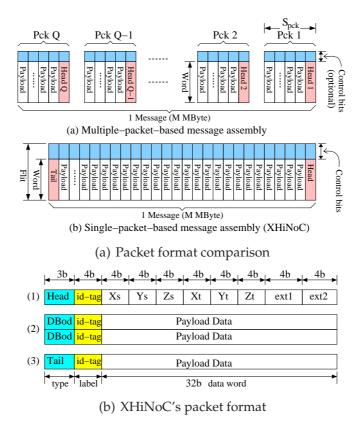

| 4.4  | (a) Comparisons of multiple-packet-based and single-packet-based message assembly, and (b) the XHiNoC packet format                   | 91  |

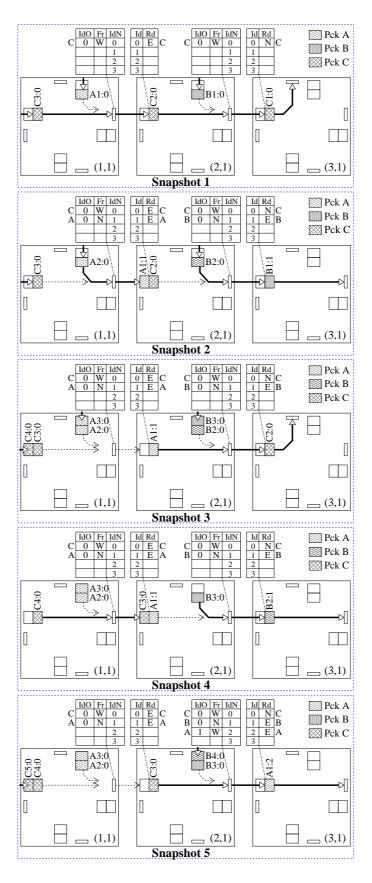

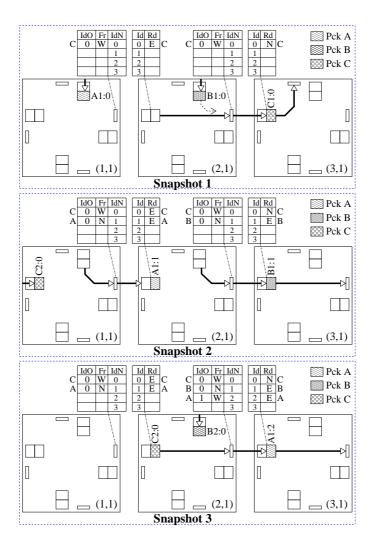

| 4.5  | Switching behavior in saturation                                                                                                      | 94  |

| 4.6  | Switching behavior in non-saturation                                                                                                  | 95  |

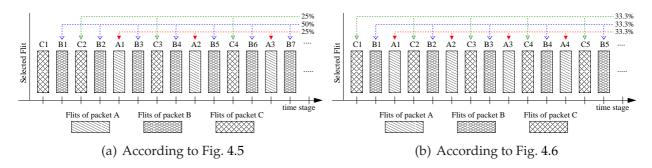

| 4.7  | Flits output/outgoing selection results at East output port in the router node (2,1)                                                  | 97  |

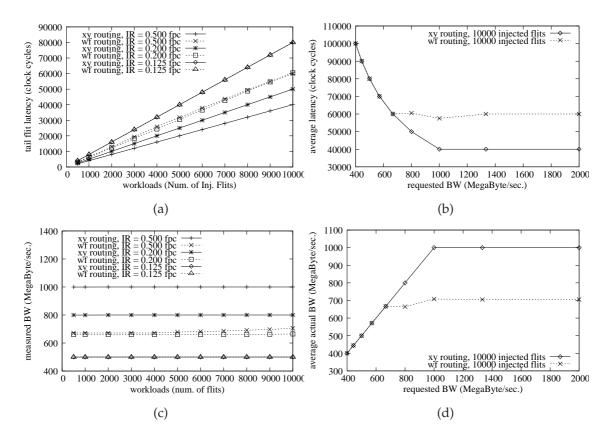

| 4.8  | Latency and bandwidth measurements in bit complement traffic scenario                                                                 | 98  |

| 4.9  | Measurement of the actual injection and acceptance rate at two selected communication pairs using static XY routing                   | 99  |

| 4.10 | Measurement of the actual injection and acceptance rate at two selected communication pairs using minimal adaptive West-First routing | 100 |

| 4.11 | Latency and bandwidth measurements in hotspot traffic scenario                                                                        |     |

TABLE OF CONTENTS xxiii

| 4.12 | Measurement of the actual injection and acceptance rate at two selected communication pairs using static XY and minimal adaptive West-First routing |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13 | Latency and actual bandwidth measurements in transpose traffic scenario 103                                                                         |

| 4.14 | Latency and actual bandwidth measurements in perfect shuffle (1-bit left-rotate) traffic scenario                                                   |

| 4.15 | Latency and actual bandwidth measurements in bit reversal traffic scenario. $105$                                                                   |

| 4.16 | Crossbar switch structure for fully and customized IO interconnects $108$                                                                           |

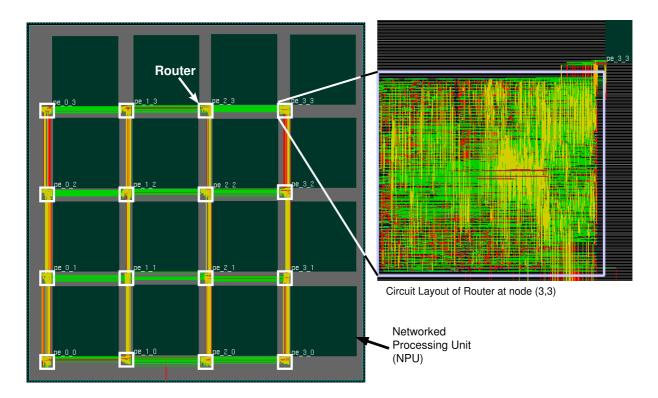

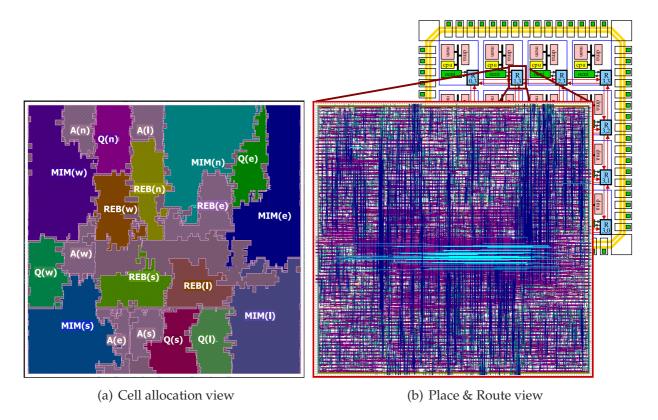

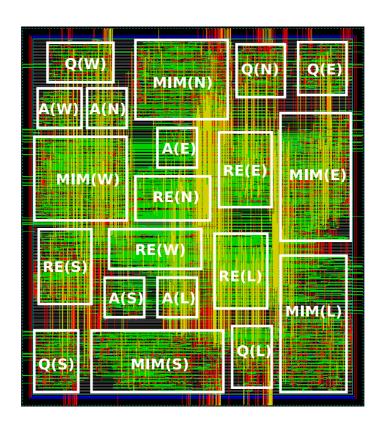

| 4.17 | Circuit layout of a multiprocessor system interconnected with XHiNoC routers using CMOS standard-cell technology library                            |

| 4.18 | Circuit layout of the router with XY routing algorithm ( $e$ =east, $n$ =north, $w$ =west, $s$ =south, $l$ =local, $Q$ =FIFO queue, $A$ =Arbiter)   |

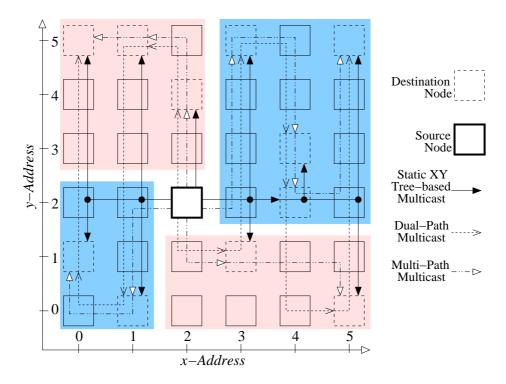

| 5.1  | The traffic formations by using static tree-based, dual-path and multi-path multicast routing methods                                               |

| 5.2  | Multicast deadlock configurations when using tree-based and path-based multicast routing in mesh networks                                           |

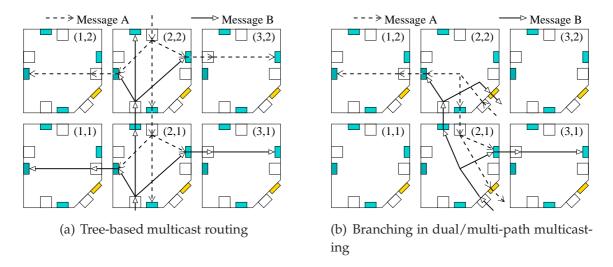

| 5.3  | Hold and Release Multicasting Policy                                                                                                                |

| 5.4  | High multicast traffic contentions in a router and solution with the Hold and Release Multicasting Policy                                           |

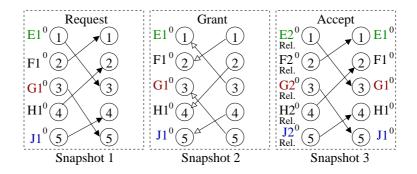

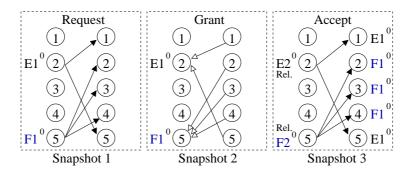

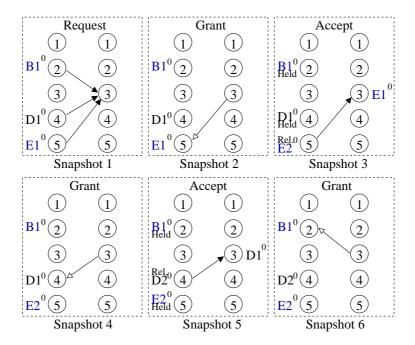

| 5.5  | Scheduling unicast requests without contention                                                                                                      |

| 5.6  | Scheduling multicast requests without contention                                                                                                    |

| 5.7  | Scheduling unicast requests with contention                                                                                                         |

| 5.8  | Specific multicast packet format                                                                                                                    |

| 5.9  | Multicast Routing Phases                                                                                                                            |

| 5.10 | Local ID-tag update for multicast header flits                                                                                                      |

| 5.11 | Mesh-Planar-based network and possible minimal planar adaptive routing paths                                                                        |

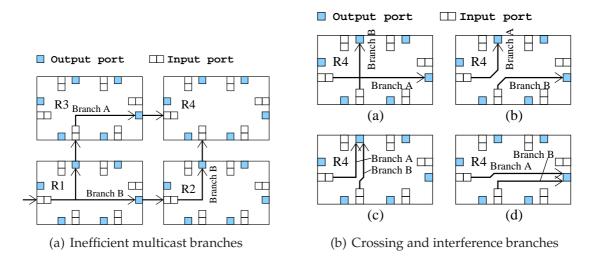

| 5.12 | Inefficient branches of multicast tree problem                                                                                                      |

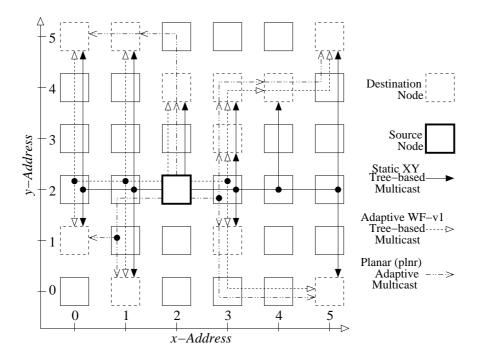

| 5.13 | The traffic formations by using static tree-based, minimal adaptive west-first and minimal planar adaptive multicast routing methods                |

| 5.14 | Distribution of the source-destination communication partners 148                                                                                   |

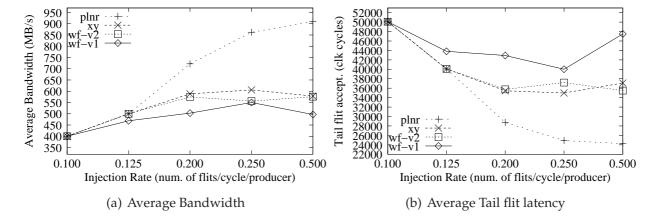

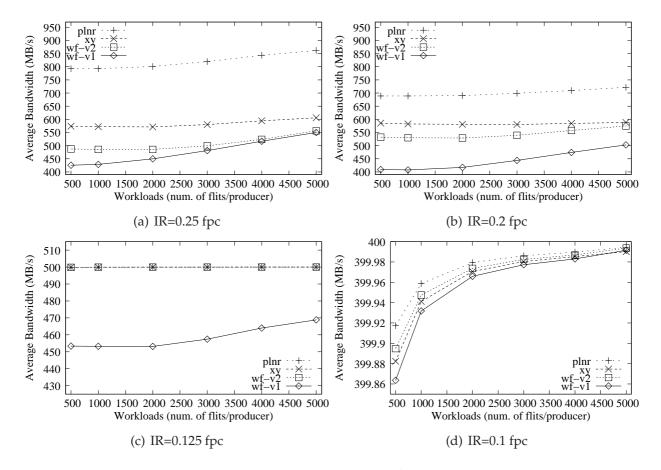

| 5.15 | Average bandwidth and tail flit acceptance latency measurement versus expected data injection rates for multicast random test scenario 149          |

| 5.16 | Average actual bandwidth versus workloads for multicast random test scenario                                                                        |

XXIV TABLE OF CONTENTS

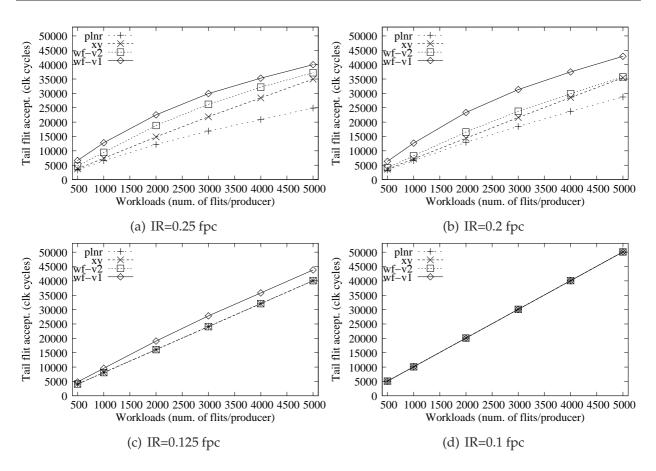

| 5.17 | Tail flit acceptance latency versus workloads for multicast random test sce-                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | nario                                                                                                                                                                                                                                        |

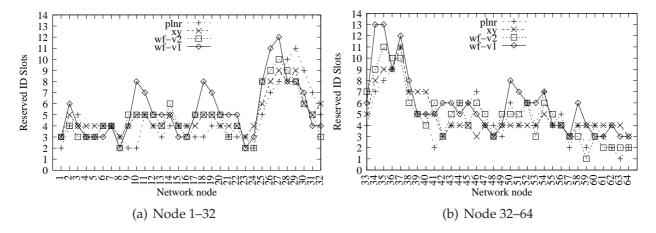

| 5.18 | Reserved (used) total ID slots for multicast random test scenario 152                                                                                                                                                                        |

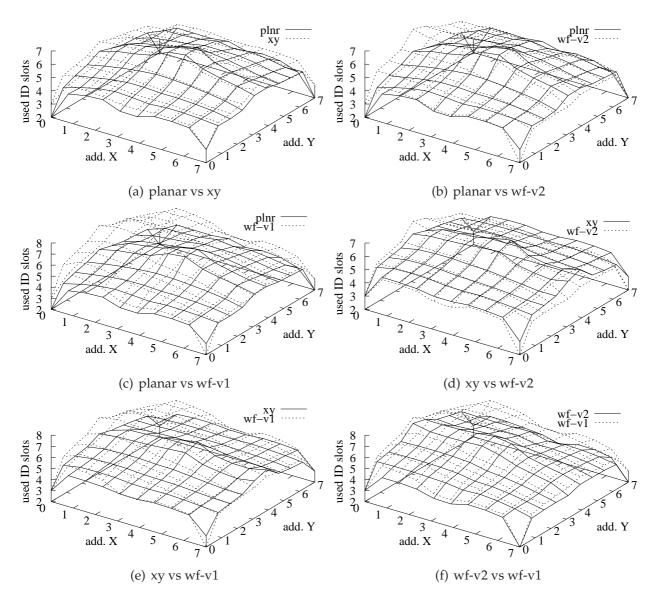

| 5.19 | 3D views of the total ID slot reservation on every NoC router for multicast random test scenario                                                                                                                                             |

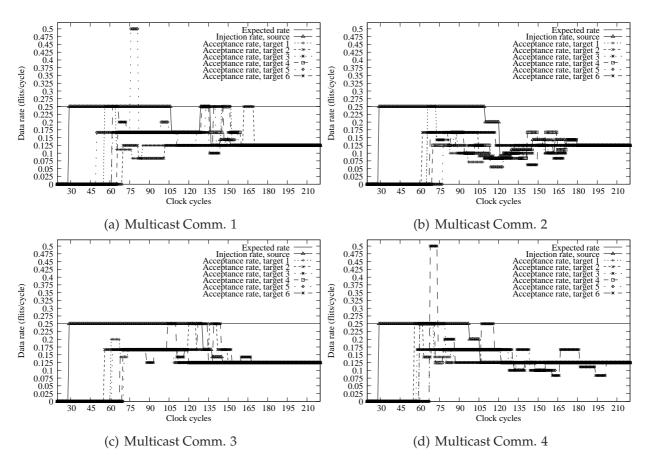

| 5.20 | Expected, actual injection rate at source node, and actual acceptance rates at multicast target nodes during NoC saturating condition by using the static tree-based multicast router (Expected injection rate is 0.25 flits/cycle). 155     |

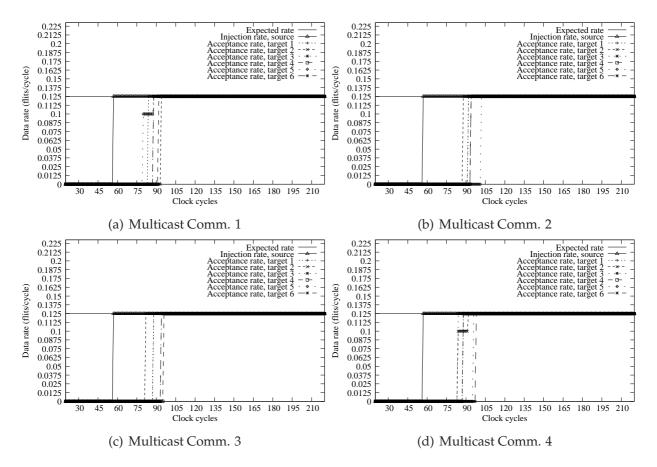

| 5.21 | Expected, actual injection rate at source node, and actual acceptance rates at multicast target nodes during NoC non-saturating condition by using the static tree-based multicast router (Expected injection rate is 0.125 flits/cycle).156 |

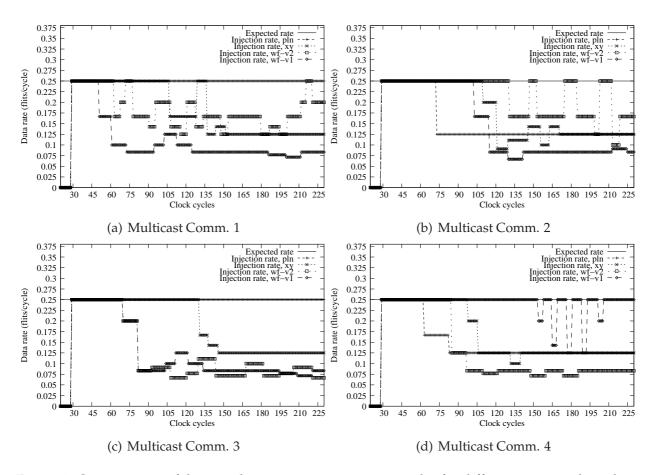

| 5.22 | Comparisons of the actual injection rates at source nodes for different routing algorithms during NoC saturating condition (Expected injection rate is 0.25 flits/cycle)                                                                     |

| 5.23 | Circuit layout of the XHiNoC router with tree-based XY multicast routing using CMOS standard-cell technology library                                                                                                                         |

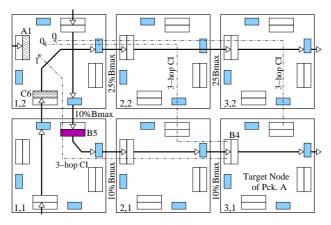

| 6.1  | Problem in the unpredictable two-hop neighbor-on-path congestion measurement                                                                                                                                                                 |

| 6.2  | A Situation of 2-hop and 3-hop congestion information (CI) traceback and actual link bandwidth consumption                                                                                                                                   |

| 6.3  | Another Situation of 2-hop and 3-hop congestion information (CI) trace-back and actual link bandwidth consumption                                                                                                                            |

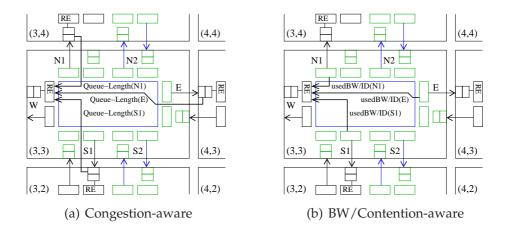

| 6.4  | Alternative information that can be used to make adaptive output routing selection                                                                                                                                                           |

| 6.5  | Switch microarchitectures for routers with contention- and bandwidth-aware and with congestion- and contention-aware adaptive routing selection strategy                                                                                     |

| 6.6  | Packet format for the CBWA and BWA adaptive routing selection strategy 174                                                                                                                                                                   |

| 6.7  | ID-based routing table reservation and assignment                                                                                                                                                                                            |

| 6.8  | Local ID slot reservation                                                                                                                                                                                                                    |

| 6.9  | Average and actual bandwidth measurement per target node under transpose scenario in $4 \times 4$ mesh network                                                                                                                               |

| 6.10 | The tail flit acceptance measurement on every target node in clock cycle period under transpose scenario in $4 \times 4$ mesh network                                                                                                        |

| 6.11 | Average tail flit acceptance latency under transpose scenario in $4 \times 4$ mesh NoC                                                                                                                                                       |

TABLE OF CONTENTS XXV

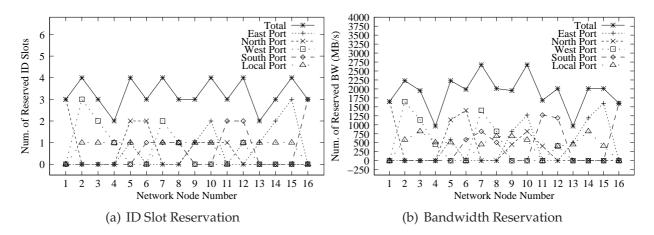

| 6.12 | Bandwidth space reservation at each output port under transpose scenario in $4 \times 4$ mesh NoC                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.13 | ID slots reservation at each output port using transpose scenario in $4\times 4$ mesh NoC                                                                 |

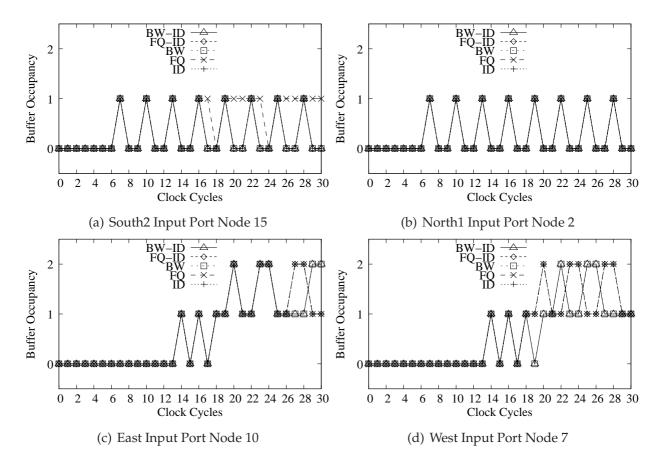

| 6.14 | FIFO Queue occupancy at selected output ports and network nodes for transpose scenario in 4x4 mesh NoC                                                    |

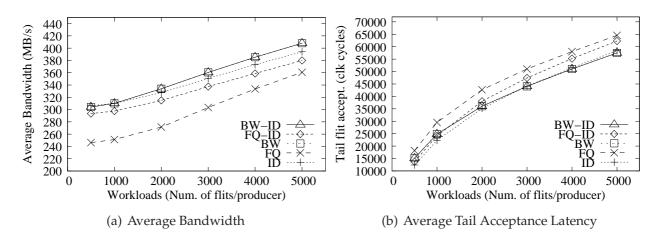

| 6.15 | Average bandwidth measurement and tail acceptance delay for bit-complement scenario in $8\times 8$ mesh network                                           |

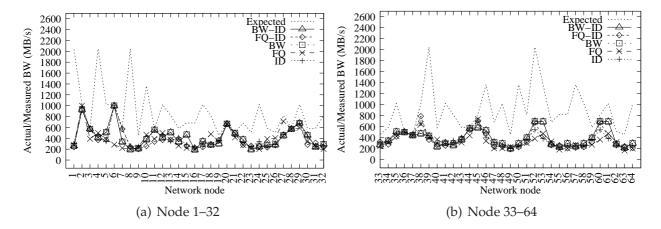

| 6.16 | Actual bandwidth measurement per network node for bit complement scenario in $8\times 8$ mesh network                                                     |

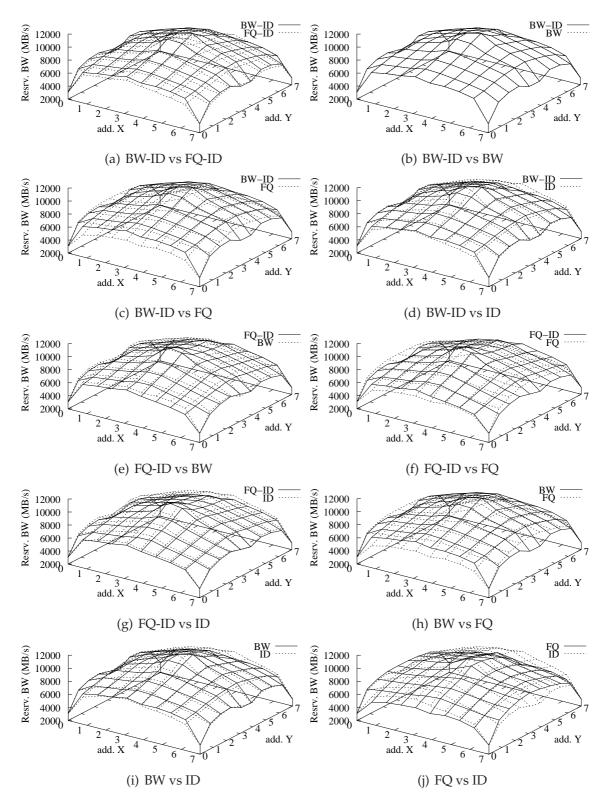

| 6.17 | Distribution of the total bandwidth reservation on every network node for bit-complement scenario in $8\times 8$ mesh NoC                                 |

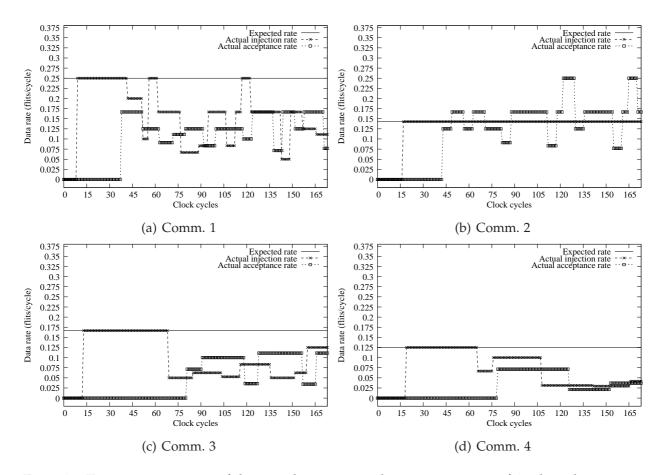

| 6.18 | Transient responses of the actual injection and acceptance rates of 4 selected communication pairs for bit-complement traffic scenario using BW-ID method |

| 6.19 | Transient responses of the actual injection and acceptance rates of 4 selected communication pairs for bit-complement traffic scenario using FQ-ID method |

| 7.1  | State-of-the-Art of the data multiplexing techniques for NoCs 190                                                                                         |

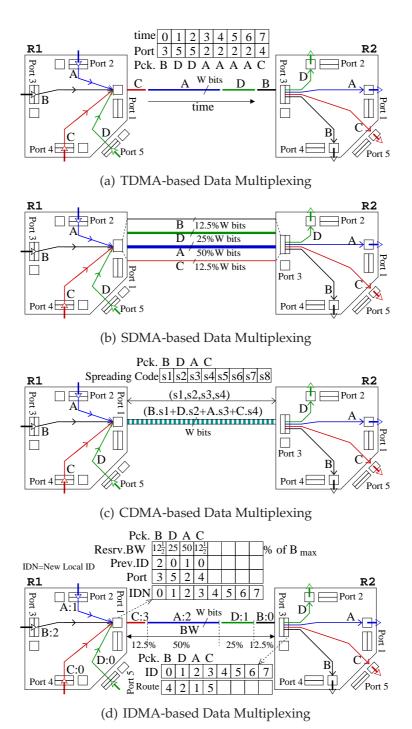

| 7.2  | Connection setup method using time slot TDMA-based and the IDMA-based methods                                                                             |

| 7.3  | Connection-oriented multicast routing protocol                                                                                                            |

| 7.4  | Deadlock configuration when enabling backtrace                                                                                                            |

| 7.5  | Autonomous runtime local ID slot reservation allowing conflict of multicast headers                                                                       |

| 7.6  | Conflict management and link sharing for contenting multicast payload flits.198                                                                           |

| 7.7  | Local ID slot reservation (indexing) and routing table slot reservation (indexing)                                                                        |

| 7.8  | Node-to-node traffic flow for an on-chip radio system and the bandwidth measurement results                                                               |

| 7.9  | One of many possible runtime local ID slot reservation configurations for Communication $a-j$ and Communication $k$                                       |

| 7.10 | Number of bandwidth reservations at each outgoing port of all 16 network nodes                                                                            |

| 7.11 | Generic router architecture                                                                                                                               |

| 7.12 | Example of the general components in the West incoming and outgoing port.204                                                                              |

XXVI TABLE OF CONTENTS

| 7.13 | The detail components in the incoming port                                                               |

|------|----------------------------------------------------------------------------------------------------------|

| 7.14 | Mixed GT-BE message data transmissions in the transpose traffic scenario $206$                           |

| 7.15 | The transfer latency (delay of acceptance) of the header, response and the first databody flits          |

| 7.16 | The tail acceptance delays with different workload sizes for each communication pair                     |

| 7.17 | The actual communication bandwidth measurement with different workload sizes for each communication pair |

| 7.18 | The distribution of the ID slots and bandwidth reservation at each output port of the router nodes       |

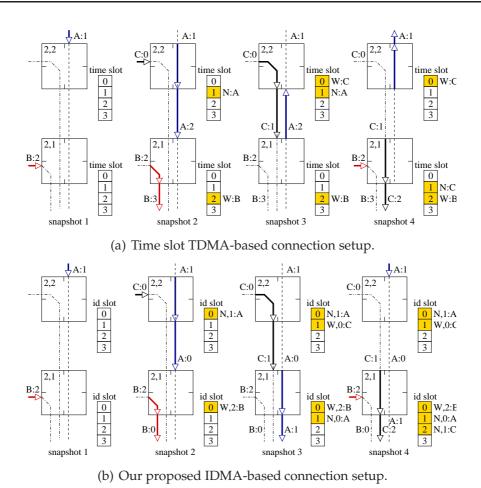

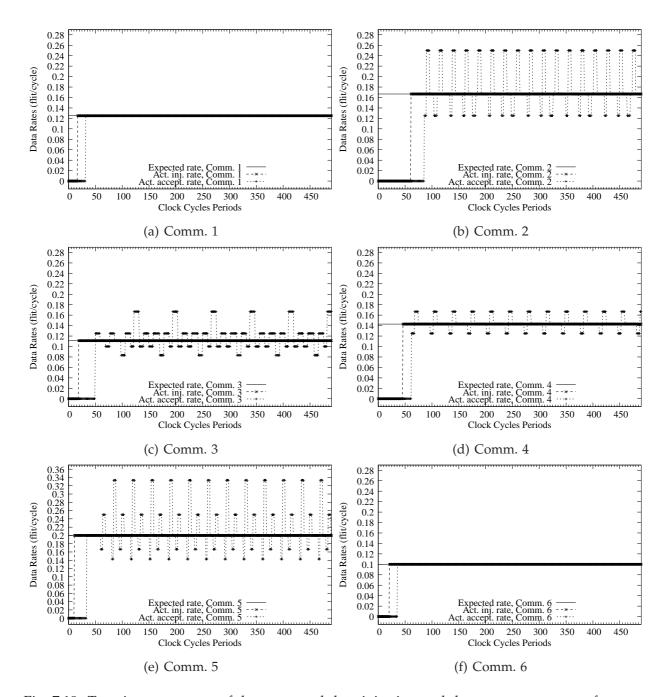

| 7.19 | Transient responses of the measured data injection and data acceptance rates for communication 1–6       |

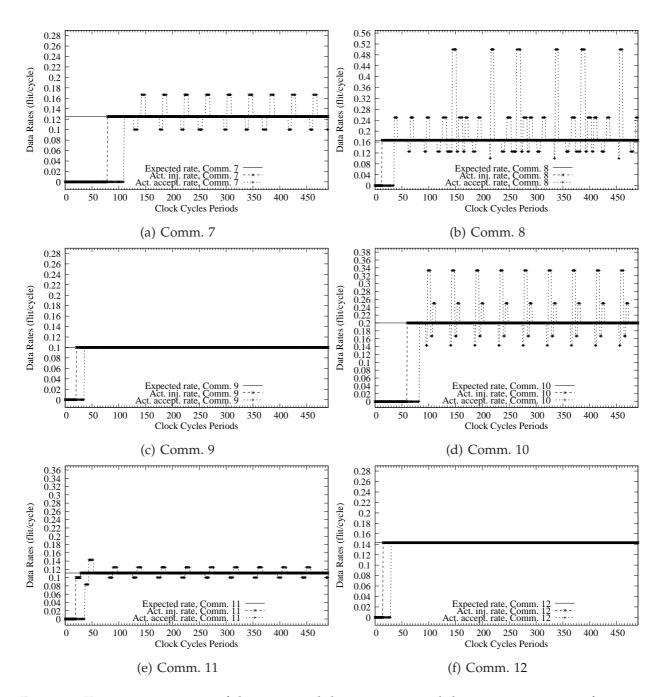

| 7.20 | Transient responses of the measured data injection and data acceptance rates for communication 7–12      |

# **List of Algorithms**

| 1  | Static X-First (XY) Routing Algorithm                             |

|----|-------------------------------------------------------------------|

| 2  | Minimal Adaptive West-First (WF) Routing Algorithm                |

| 3  | Minimal Adaptive Negative-First (NegF) Routing Algorithm 28       |

| 4  | Minimal Adaptive North-Last (NL) Routing Algorithm                |

| 5  | Minimal Adaptive Routing Algorithm with VCs for 2 Sub-Networks 33 |

| 6  | First-In First-Out Queue                                          |

| 7  | Runtime ID-based Routing Mechanism                                |

| 8  | Rotating Flit-by-Flit Arbitration                                 |

| 9  | Runtime Local ID-tag Update                                       |

| 10 | Runtime ID-based Multicast Routing Mechanism                      |

| 11 | Runtime Local ID-tag Update for Multicast Routing                 |

| 12 | 2D Planar Adaptive Routing Algorithm                              |

| 13 | Multicast Adaptive Routing Selection Strategy (Abstract view) 147 |

| 14 | Multicast Adaptive Routing Selection Strategy (Logical view) 147  |

| 15 | CBWA Adaptive Routing Function–BW-ID version (Abstract view) 169  |

| 16 | CBWA Adaptive Routing Function–BW-ID version (Logical view) 171   |

| 17 | CCA Adaptive Routing Function–FQ-ID version (Logical view) 171    |

| 18 | Bandwidth-Aware Adaptive Routing Function (Logical view) 172      |

| 19 | Congestion-Aware Adaptive Routing Function (Logical view) 172     |

| 20 | Contention-Aware Adaptive Routing Function (Logical view) 173     |

## **Abbreviations**

2D : 2-dimension 3D : 3-dimension

API : Application Programming Interface

Arb : Arbiter/Arbitration Unit

ASIC : Application-Specific Integrated Circuit

ARM : Advanced RISC Machine

BE : Best-Effort BW : Bandwidth

BWA : Bandwidth-Aware

BWS : Buffered Wormhole Switching

CAD : Computer-Aided Design

CBWA : Contention- and Bandwidth-AwareCCA : Contention- and Congestion-AwareCDMA : Code-Division Multiple Access

CI : Congestion Information

CMOS : Complementary Metal Oxide Silicon

CMP : Chip-Level Multiprocessor

CPU : Central Processing UnitCRC : Cyclic Redundancy Check

DSM : Distributed Shared Memory

DSP : Digital Signal ProcessorDVB : Digital Video Broadcasting

FIFO : First-In First Out fpc : flits per cycle

FPGA : Field Programmable Gate Array

GALS: Globally-Asynchronous Locally-Synchronous

GB: Guaranteed-Bandwidth

GPU: Graphics Processing Unit

GS: Guaranteed-Service

GT : Guaranteed-Throughput

XXX TABLE OF CONTENTS

HPF : High Performane FortranHPC : High Performane Computing

IC : Integrated Circuit

IEEE : Institute of Electrical and Electronics Engineers

IDMA : Identity-Division Multiple Access

ID-tag : Identity-tag

IP : Intelectual Property

ITRS : International Technology Roadmap for Semiconductors

LC : Link Controller

MAC : Medium Access ControlMCU : Micro-Controller Unit

MIM : Multiplexor with ID Management Unit

MIPS : Microprocessor without Interlocked Pipeline Stages

MPI : Message Passing Interface

MPSoC : Multiprocessor System-on-Chip

NegF : Negative First

NI : Network Interface

NL : North-Last

NoC : Network-on-Chip

OCNI : On-Chip Network Interface

OpenMP: Open Multi Processing

OSI : Open System Interconnection PCS : Pipelined Circuit Switching

PE : Processing Element

PVM : Parallel Virtual Machine

QoS : Quality of Service

RAM : Random Access Memory

RE : Routing Engine

REB : Routing Engine with Data BufferingRFIC : Radio Frequency Integrated CircuitRISC : Reduced Instruction Set Computing

RSM : Routing State Machine

RRT : Routing Reservation Table

RTL : Register Tansfer Level

TABLE OF CONTENTS XXXI

SAF : Store-And-Forward SEU : Single-Event Upset

SMT : Symmetric Multi-Threading

SDMA : Spatial-Division Multiple Access

SoC : System-on-Chip

SVC : Switched-Virtual Circuit

TDMA : Time-Division Multiple Access

TPG : Traffic Pattern GeneratorTRE : Traffic Response Evaluator

TSV : Through Silicon Via

ULSI : Ultra Large Scale Integration

VC : Virtual Channel

VCT : Virtual Cut-Through

VLSI : Very Large Scale Integration

WF : West-First

WiFi : Wireless Fidelity

WiMAX : Worldwide Interoperability for Microwave Access

XHiNoC: eXtendable Hierarchical Network-on-Chip

## **Symbols**

```

B_{max}

: Maximum bandwidth capacity of a link

F_n(t,i): A flit with type t and ID-tag i from input port n

b_{type}

: bit-width for the type field in each flit

: bit-width for the ID-tag field in each flit

b_{tag}

: bit-width for the dataword field in each flit

b_{word}

N_{hf}

: Number of header flits in a multicast message

N_{dest}

: Number of destination nodes for a multicast message

: Number of router node in a NoC

N_{node}

: Set of routers \{R_1, R_2, \cdots, R_{N_{node}}\}

\Re

R_c

: Router node c, where R_c \in \Re

Λ

: Set of communication links in a NoC

L_{i,j}

: Link connecting R_i to R_j, where L_{i,j} \in \Lambda

N_{inp}

: Number of input ports in a router

: Number of output ports in a router

N_{outp}

Φ

: Set with input port elements \{1, 2, \dots, N_{inp}\}

: Set with output port elements \{1, 2, \cdots, N_{outp}\}

\varphi

: Input port number, n \in \Phi

n

: Output port number, m \in \varphi

m

: Number of requests to acquire output port m

N_{s,n}^{req}

: Number of requests from input port n

\varphi_n^{req}

: Set of active routing requests from an input port n

\Phi_m^{req}

: Set of active routing requests to an output port m

: Number of ID Slot on every link

N_{slot}

Γ

: Set of elements \{0, 1, 2, \dots, N_{slot} - 1\}

: Set of flit type element {header, databody, tail, response}

\varepsilon_{type}

: Type of a flit, type \in \varepsilon_{type}

type

Ω

: Set of ID slots elements \{0, 1, 2, \cdots, N_{slot} - 1\}

ID, k

: Local ID-tag and ID slot, k \in \Omega, \Omega \subseteq \Gamma

```

XXXIV TABLE OF CONTENTS

$f_{RSM}$ : Routing Function made by a Routing State Machine

$f_{IDM}$ : ID-tag Update Function made by an ID-Management Unit

$ID_{old}$  : old/previous ID-tag

$ID_{new}$ : new ID-tag after update function

$N_{usedID}$ : Number of used/reserved ID slot in the ID Slot Table

$N_{usedBW}$ : Number of used/reserved bandwidth on an outgoing link

$r_{dir}$ : Routing direction (decision)

$A_{dest}$ : Address of a destination node

R(t) : Routing Request Matrix  $r_{n,m}(t)$  : Matrix element of R(t)

A(t) : Arbitration (Routing Acknowledge) Matrix  $T_{s,m}$  : Rotating arbitration time at output port m

$a_{n,m}(t)$  : Matrix element of A(t)  $R^*(t)$  : Tagged Request Matrix  $r_{n,m}^*(t)$  : Matrix element of  $R^*(t)$

$S^k$ : State of Id Slot k, where  $k \in \Omega$

S(k) : ID Slot Table

T(k): Routing Reservation Table with slot number k

$M_n$ : Routing Machine at input port n

$T_n$ : Routing Reservation Table at input port n

$E_n$ : Routing Engine at input port n

usedID(m): Number of reserved ID at output port m

usedBW(m): Number of reserved bandwidth at output port m

## Chapter 1

## **Introduction and Overview**

#### **Contents**

| 1.1 | Background and Motivations    | 1 |

|-----|-------------------------------|---|

| 1.2 | Research Scope and Objectives | 3 |

| 1.3 | Thesis Outline                | 4 |

### 1.1 Background and Motivations

According to the International Technology Roadmap for Semiconductors (ITRS) [105], the transistor feature size will be smaller in submicron (nanometer) scale and integrated circuits operate below one volt. Since the feature size of newer technology is smaller, the integrated circuits using this new technology can then be clocked faster. The smaller transistor feature size also enables the integration of more tansistors on a single die. The challenges related to the progress of the advanced technology are design concepts and design methodologies that can make use of such new technology. The most attractive thing of the new and smaller technology is the reduced cost. As the technology evolves toward the production of larger and larger circuit functions on a single die and unit cost falls as the number of component per circuit rises, then the cost advantage will continue to increase [160].

System-on-chip (SoC) design methodology is one of the potential solutions for system level design. The SoC design method is based on design reuse method which is acceptable in industry and compatible with industrial standard computer-aided design (CAD) tools. As the feature size of a CMOS technology decreases, the working frequency of the SoC system can be increased in order to improve the system performance. However, this popular technique has run out of steam, due to excessive power consumption, heat dissipation and electro-migration reliability issues [54]. Hence, solving a very complex computation by participating more computing elements will be a preferable solution. SoC architecture paradigm will potentially move from single processing element to multiple

processing elements [31], which is called as a multiprocessor SoC (MPSoC).

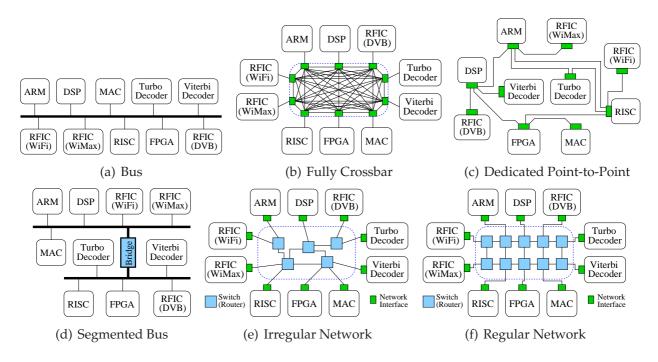

Traditionally, a SoC or an MPSoC system interconnects intellectual properties (IP) components by using a *bus-based interconnect system*. When the number of participating components is more than ten, then the bus system will have a performance bottleneck problem [106]. In order to solve the performance bottleneck problem, a *fully crossbar interconnect* can be used. However, this approach will implicate a wiring complexity in the circuit, in which wires could be more dominant than the logic parts, especially when the number of the interconnected components is very high. Another problem in the fully crossbar interconnect is the effect of electromagnetic interference that can disturb the interconnect functionality. A *point-to-point interconnect* (*dedicated wires*) is also another alternative solution to the performance bottleneck problem and to the wiring complexity problem. However, this approach is not flexible. Instead of connecting the top-level components by routing the dedicated wires, an *on-chip interconnection network* can be implemented and interconnect the interacting components by routing packets through the network [59].

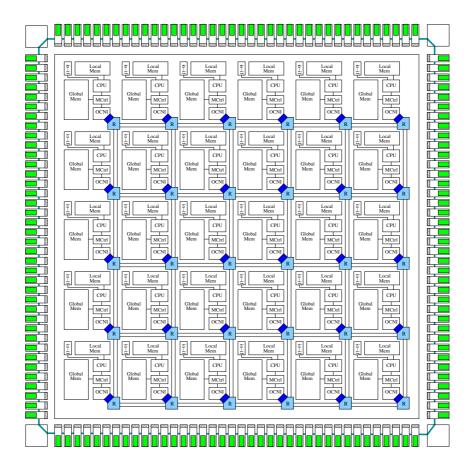

Since interconnect technology affects more profoundly on chip performance and power usage, improving on-chip communication technology has become increasingly important to researchers and processor manufacturers [78]. A high-throughput communication infrastructure is required to meet the bandwidth requirement of each data communication flows generated due to interacting processors in the MPSoC systems. This issue can be potentially handled by a communication infrastructure based on the *network-on-chip* (NoC), which has better scalability to provide sufficient communication bandwidth.

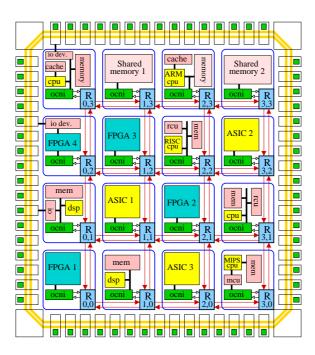

On-chip network infrastructure also enables advanced intellectual properties (IP) communication concepts for MPSoC. In embedded MPSoC systems, NoCs can provide a flexible communication infrastructure, in which several components such as microprocessor cores, MCU, DSP, GPU, memories and other intellectual property (IP) components can be interconnected by using reusable NoC routers via general modular interfaces. The MPSoC systems can also be reconfigured for a certain embedded computing application and can be customized to improve the communication performance in the application. Hence, the NoC-based systems combine performance with design modularity [176]. The innovation of a flexible NoC communication infrastructure will enable accordingly the IP vendors to sell not only their IP components but also a system architecture [54].

The main component of the NoC system is an *on-chip router* (*switch*). Research in the field of off-chip interconnection network is not a new activity. The off-chip interconnection network has been a mature technology. However, there are some issues that should be addressed regarding the adoption of the "off-chip network" concepts into the "on-chip network" implementations. We are sure that the new innovations related to switching method, adaptive routing algorithm, network flow control and buffering scheme suitable for NoCs are still required. Until now, there is no standard for the NoC architecture similar to that of the internet world. This thesis is motivated to provide a new switching method, new adaptive routing strategies and a new deadlock-free theory and methodol-

ogy for tree-based multicast routing and its VLSI implementation, which are in any case different from the existing methods mentioned in the literature and suitable for NoCs.

## 1.2 Research Scope and Objectives

The research scope of this thesis are the concept of VLSI architecture and implementation of on-chip routers with advantageous features and characteristics to develop networks-on-chip for multiprocessor systems. Since the main focus of the research is the NoC routers design concept, then this thesis will discuss some issues and aspects of the NoC router architecture and its supporting modular components. Therefore some topics such as switching method, routing algorithm, network flow control, and the internal NoC router pipeline microarchitecture including its pipeline control are the main scopes of this thesis.

The research experiments on the NoC-based multiprocessor systems equipped with a programming model, and application programming interface (API) of the multiprocessor system with distributed memory architecture are part of the research interests conducted in our institute. However, the designs of NoC-based multiprocessor systems, on-Chip Network Interface (OCNI), and parallel programming models are beyond the scope of this thesis.

The general objective of this doctoral thesis is to present a design concept and generic architecture of a NoC prototype with specific features supporting specific services. The specific objectives of this thesis are intended to improve the existing methodology, design concepts and characteristics of NoC routers that have been developed so far in the NoC research area. The specific objectives are:

- to present a new wormhole switching method [223] [229], [237] and to show theoretically the advantageous characteristics compared to traditional wormhole switching, in which the head-of-line-blocking problem is solved without using virtual channels,

- to present a new theory for deadlock-free multicast routing algorithm [234] and to show the advantageous characteristics and VLSI implementations [224], [227], [232] compared to existing deadlock-free multicast routing methods, in which the multicast dependency (contention) problem is solved without the use of virtual channels,

- to present a new approach to design runtime adaptive routing selection strategies based on contention and bandwidth information or combination of both information, and to show their advantageous performance characteristics compared to other adaptive routing selection strategies presented in the literatures [236],

- to present a new and more flexible Switched-Virtual Circuit (SVC) configuration method to design a NoC router with connection-oriented guaranteed-bandwidth

service and to show the advantageous VLSI architecture and methodology to combine the guaranteed-throughput service with the connectionless best-effort service compared to existing methodologies presented so far in the NoC research area [221], and

• to introduce a flexible VLSI microarchitecture of a NoC communication infrastructure that can flexibly support the aforementioned novel theory and methods.

## 1.3 Thesis Outline

The remaining chapters are generally divided into three chapter groups, i.e. the introductory chapter represented by Chap. 2, the contribution chapters describing the contributions of this thesis (Chap. 3–Chap. 7), and the concluding chapter represented by Chap. 8. The brief descriptions of each chapter are shown in the following.

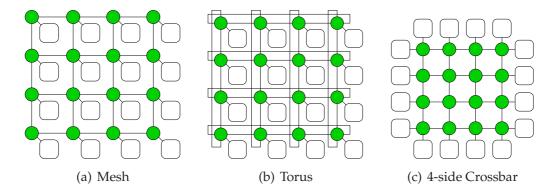

- Chap. 2. This chapter describes the general theory and basic knowledge about interconnection networks such as network topologies, generic switch architecture, switching methods (store-and-forward, virtual cut-through, wormhole, circuit switching, etc.) and routing algorithms (deterministic, adaptive). Research challenges on the design of on-chip interconnection networks as well as some research areas related to NoCs such as multicore systems, parallel programming models and NoC testing methods are also briefly presented in this chapter.

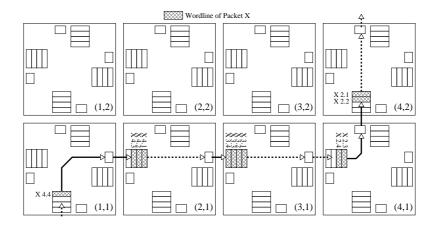

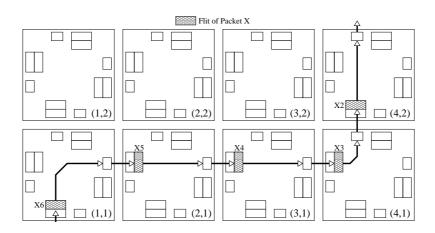

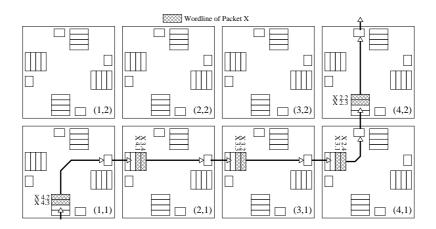

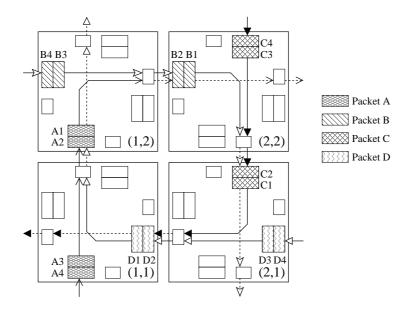

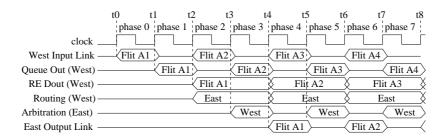

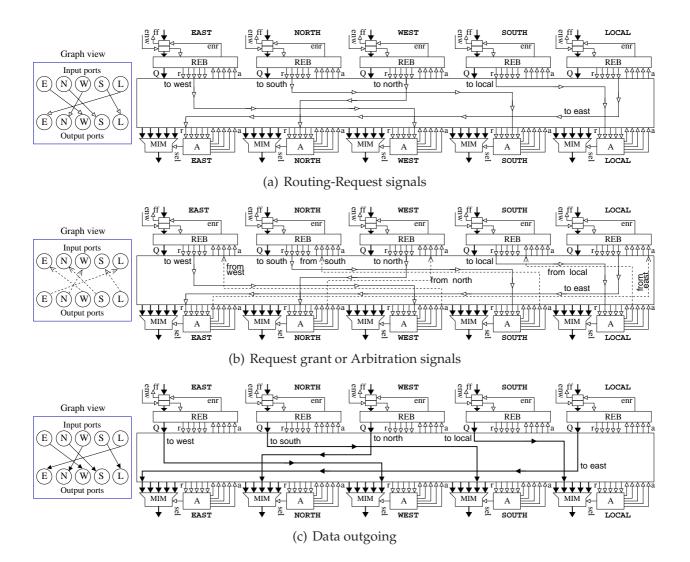

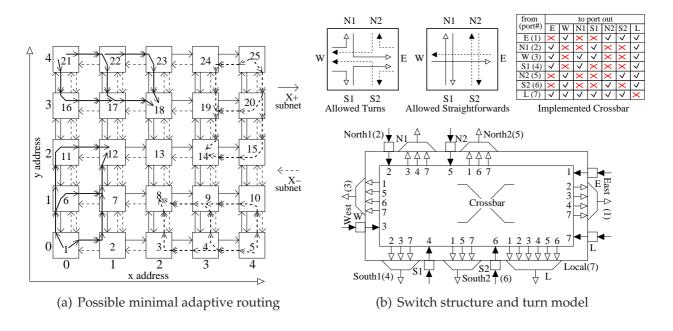

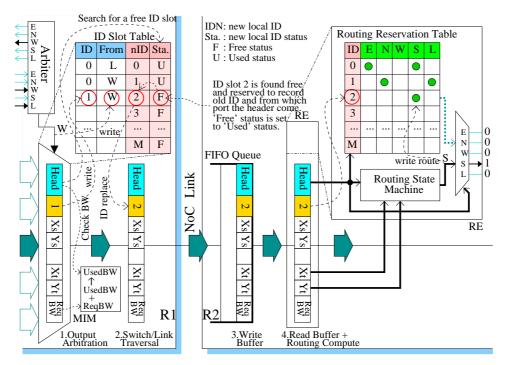

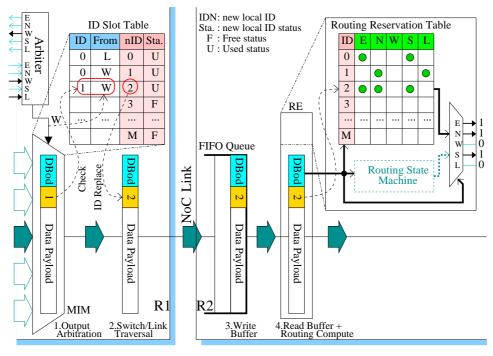

- *Chap. 3.* This chapter describes formally the generic architecture and components of a router prototype called XHiNoC, which is developed as a part of this doctoral research. The XHiNoC router prototype consists of generic components and is extendable to include some additional services with small modifications in the generic components. This chapter also presents the main concept of the XHiNoC being flexible in sharing communication media in the NoC. The concept realized is based on a tag-division multiple-access technique, in which the multiplexed messages are assigned to a local identity (ID) slot. When entering a new communication channel, the local ID slot allocation or the ID-tag assignment to the message is update dynamically at runtime. The ID-tag assignment is organized in such a way that each individual message can be identified properly, and each flit (flow control digit) of the message can be routed to its routing paths correctly. The features and characteristics of the XHiNoC, which are achieved due to the implementation of the proposed concept, are described. The main issue related to the local ID slot scalability in guaranteeing service availability for all possible considered traffics is also formally described in this chapter.

- *Chap. 4.* This chapter proposes a new wormhole switching method called "wormhole cut-through switching method", in which flits of different wormhole messages

1.3 Thesis Outline 5

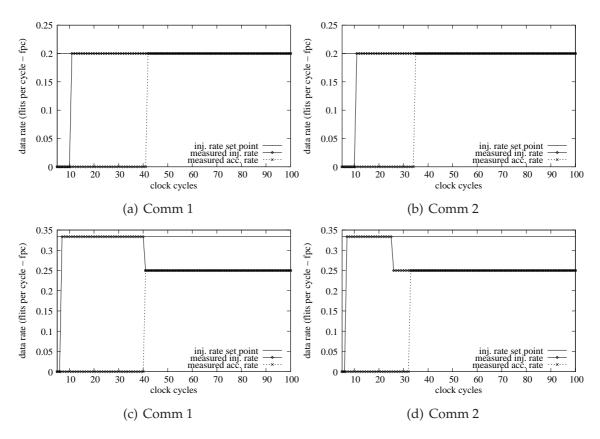

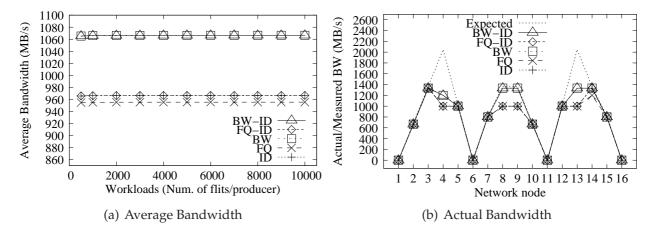

can be interleaved among each other at flit-level in the same link. The realization of the new wormhole switching is based on the main XHiNoC concept described previously in Chap. 3. The performance characteristics of the proposed switching method are evaluated under various commonly used data distribution scenarios. This chapter also shows how the head-of-line blocking problem is solved during saturating and non-saturating condition, and compares it visually with the virtualchannel-based solution. Interesting performance behaviors of the new switching method are presented during non-saturating and saturating conditions. In the nonsaturating condition, end-to-end average data rate of each individual communication can be kept constant following the expected average data rate despite the increase in the number of workload. When the expected data rate is increased such that the NoC is saturated, the actual measured injection will follow the average actual acceptance rate of each considered traffic that is reduced to a steady-state point lower than the expected data rate. Hence, because of a link-level data overflow control, all message flits injected to the source nodes can be accepted without any loss at the destination nodes.

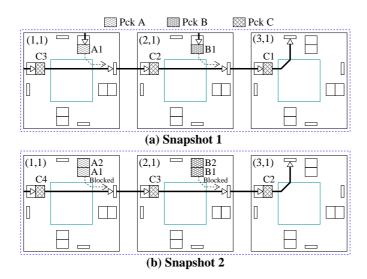

- Chap. 5. The extended version of the XHiNoC router supporting unicast and multicast services is presented in this chapter. This chapter introduces a new theory for deadlock-free multicast routing, as well as the VLSI microarchitecture of the router implementing the new deadlock-free multicast routing method. State-of-theart multicast routing methods that have been used in high performance computing arena and in NoC research area is also presented in this chapter. By using the concept presented previously in Chap. 3, combined with a "hold-release multicast tagging mechanism", oblivious multicast dependency in each router that can lead to a permanent deadlock configuration can be solved effectively. Routing algorithm used to route multicast messages is also used for unicast messages resulting in an efficient routing machine implementation. Performance comparisons of the static and adaptive tree-based multicast routing are evaluated in this chapter. This chapter also presents an output selection function to perform efficient spanning trees of the tree-based multicast routing method when using an adaptive routing algorithm.

- Chap. 6. This chapter presents new selection strategy for runtime adaptive routing based on bandwidth space reservations and contention information between alternative output directions. State-of-the-art runtime adaptive routing selection strategies is described in this chapter. Five output selection strategies are introduced, i.e. bandwidth-aware (BWA), contention-aware, congestion-aware, as well as combinations of two strategies, i.e. contention- and bandwidth-aware (CBWA), and contention- and congestion-aware (CCA) output selection functions. All output selection strategies are implemented by using the wormhole cut-through switching method and the media share concept that have been presented previously in Chap. 4 and Chap. 3, respectively. Performance evaluation and logic synthesis results from the NoC router prototypes using the adaptive routing selection strategies are also

presented in this chapter.

- Chap. 7. The extended version of the XHiNoC router supporting runtime connection-oriented guaranteed-bandwidth service for unicast and multicast messages is presented in this chapter. This chapter introduces an efficient concept for communication media sharing to configure switched virtual circuits. This chapter presents the State-of-the-art switched virtual circuit configuration methods or multiple access techniques that have been implemented so far for NoCs, including the advantages of our proposed local ID-based multiplexing techniques compared to the other techniques. An XHiNoC router prototype combining connectionless best-effort and connection-oriented guaranteed-throughput communication protocols is also introduced in this chapter.

- *Chap. 8.* The new contributions of this thesis are summarized in this chapter. The directions for future works are also briefly described in this chapter.

# Chapter 2

# **On-Chip Interconnection Networks**

| Contents                                  |                                         |                                                          |    |  |  |

|-------------------------------------------|-----------------------------------------|----------------------------------------------------------|----|--|--|

| 2.1                                       | 1 Network-on-Chip Topology Architecture |                                                          |    |  |  |

|                                           | 2.1.1                                   | Mesh-Like Network Topology                               | 13 |  |  |

|                                           | 2.1.2                                   | Tree-based Network Topology                              | 14 |  |  |

|                                           | 2.1.3                                   | Irregular or Custom Network Topology                     | 15 |  |  |

|                                           | 2.1.4                                   | Other Network Topologies                                 | 15 |  |  |

|                                           | 2.1.5                                   | Hybrid and Hierarchical Network Topology                 | 16 |  |  |

| 2.2 Generic On-Chip Switch Architecture . |                                         | ric On-Chip Switch Architecture                          | 17 |  |  |

| 2.3                                       | Switc                                   | hing Methodology                                         | 19 |  |  |

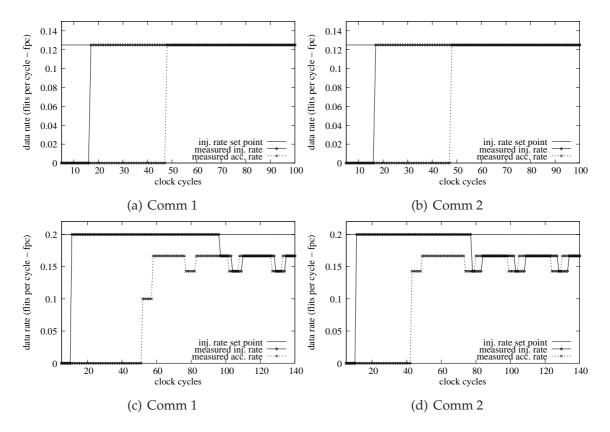

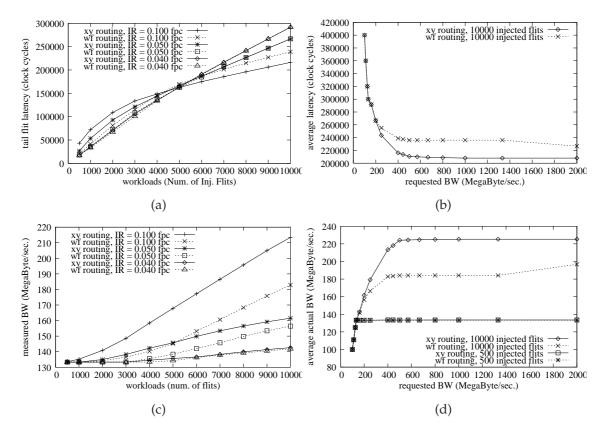

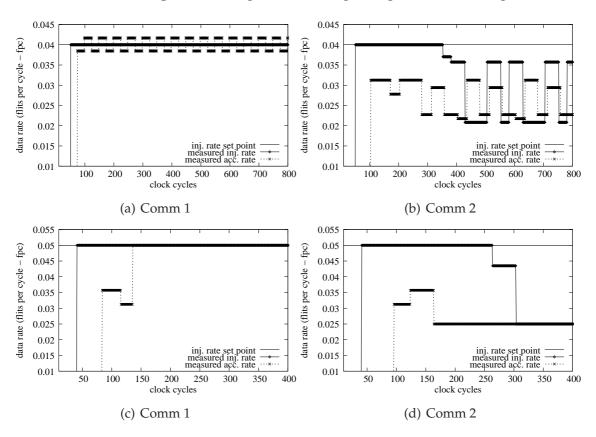

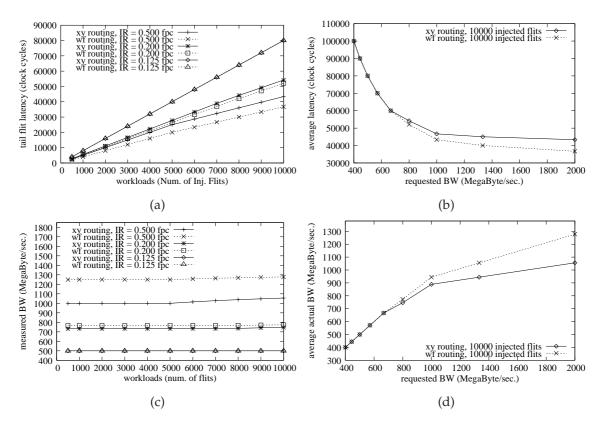

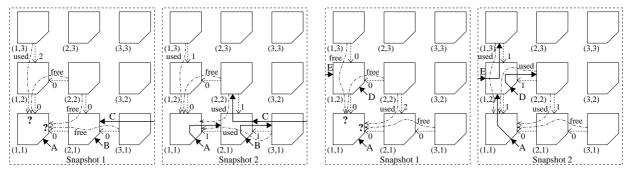

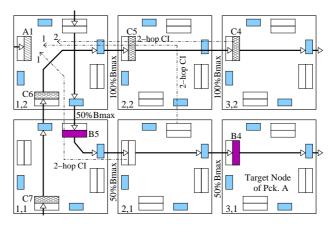

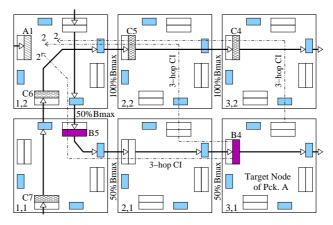

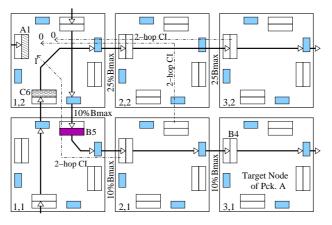

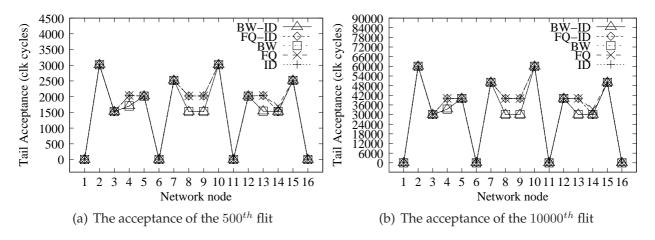

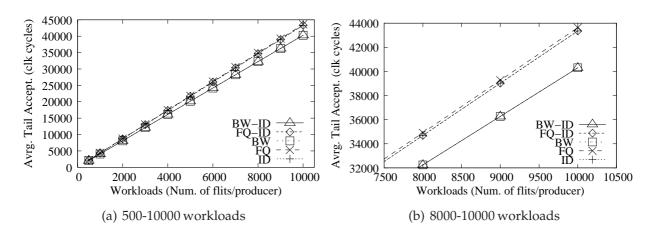

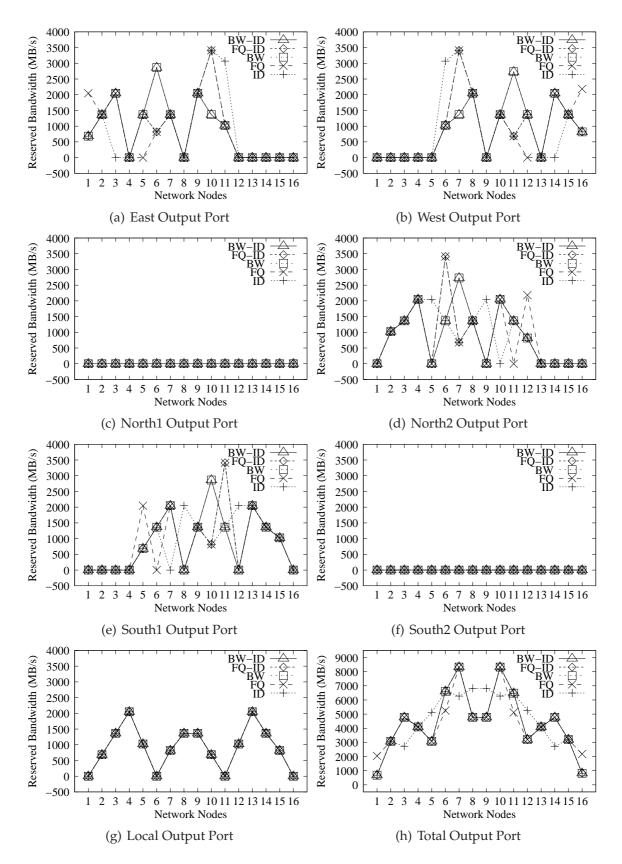

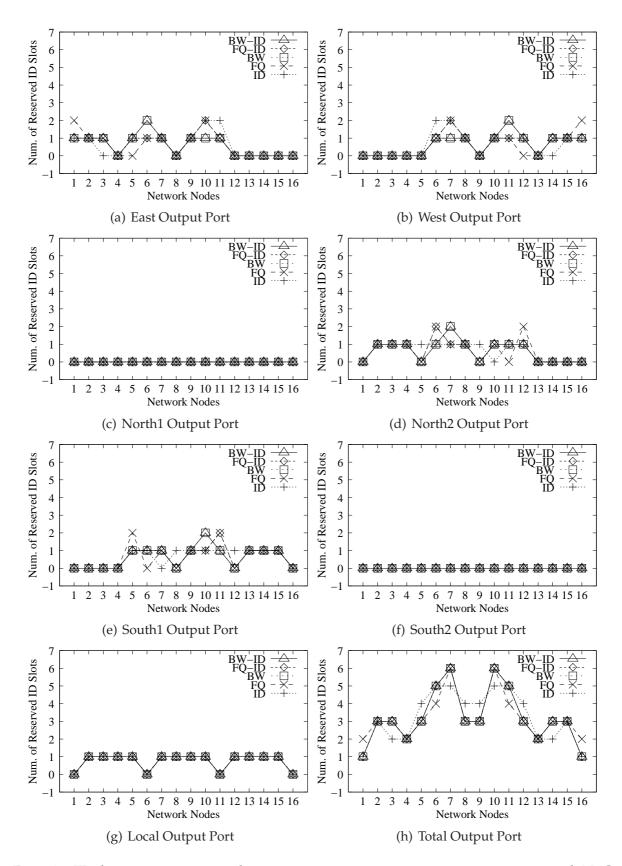

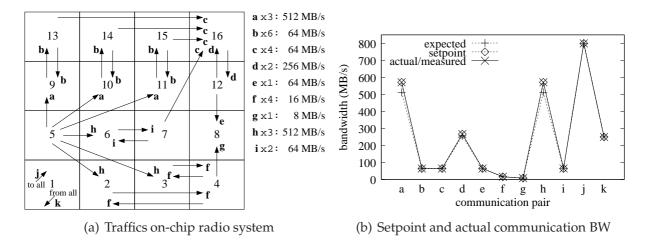

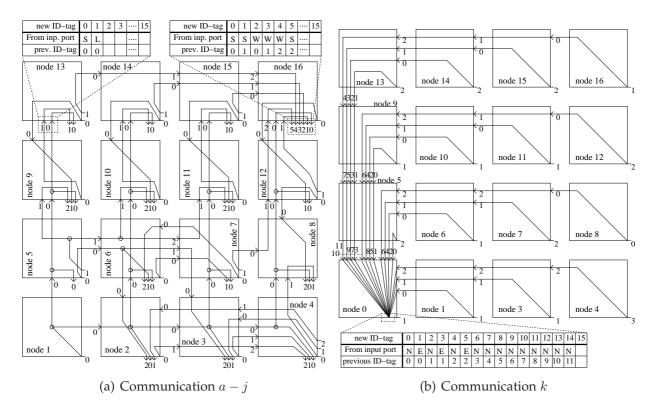

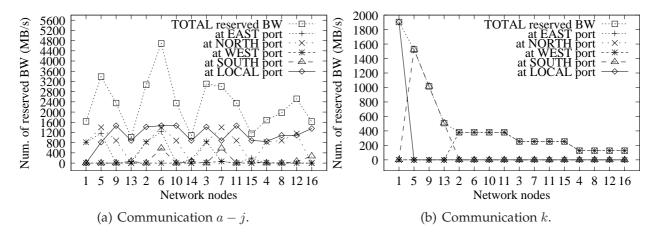

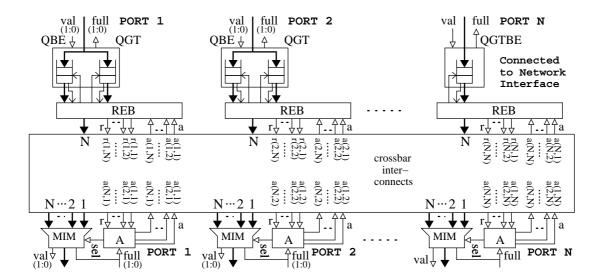

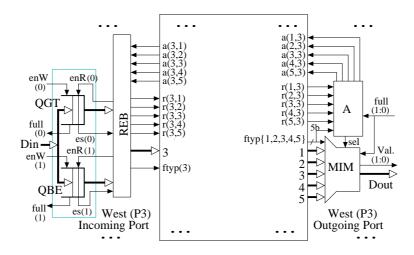

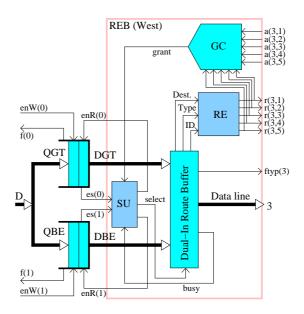

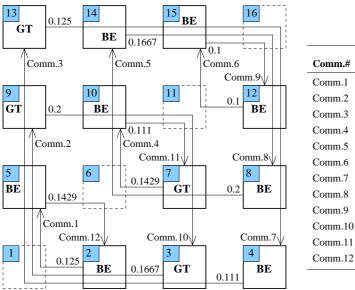

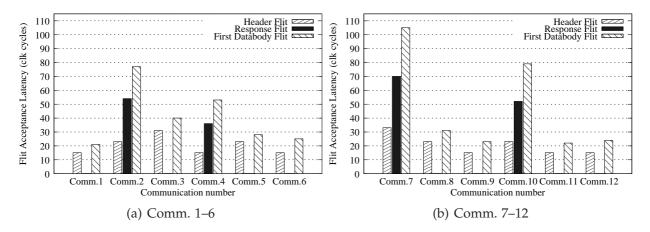

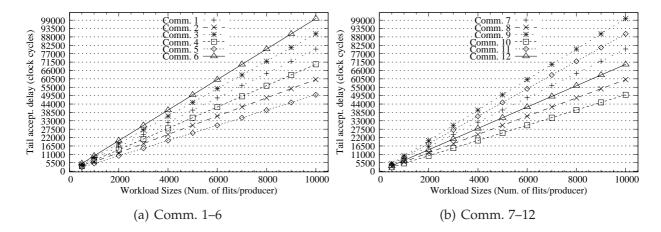

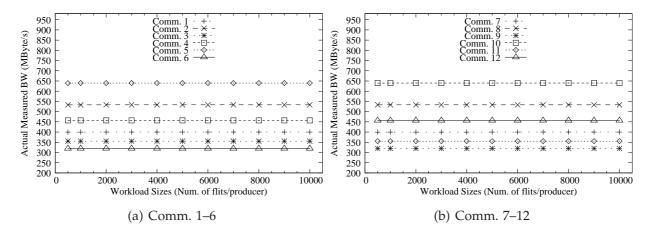

|                                           | 2.3.1                                   | Packet Switching (Store-and-Forward)                     | 19 |  |  |